## The Semistate Description of a Four Transistor CMOS Schmitt Trigger\*

A. Ahmad, R. Newcomb and F. Abedin

Microsystems Laboratory Electrical Engineering Department University of Maryland College Park, MD 20742 USA (301) 454-6869

## Abstract

In this paper we give the means for setting up the relevant semistate equations of a four transistor CMOS Schmitt trigger under development for VLSI realization. By parametrically solving the nondynamic portions of the semistate equations one sees the physical basis through which the hysteresis results. The technique is illustrated with SPICE runs.

1. Introduction

The Schmitt trigger, first introduced by

Otto Schmitt in the 1930's [1], occurs in many situations and has been basic to the operation of a number of systems, for example in reducing the effects of noise on triggering responses [2] and in describing the immune system for biological simulations [3]. It is an important enough electronic circuit element it is now treated in most texts on electronics, even at the most elementary undergraduate level [4,p.567]. However, because the basic property of the Schmitt trigger is its hysteresis, mathematical descriptions need to be formulated with care. Several mathematibased descriptions are available [5][6][7][8][9] but in using these one loses physical insight as to just why the jump for increasing input is different than for input. The situation can be decreasing improved by reverting to semistate equations [10,p.246] which allow one to give mathematical characterizations of certain types of hysteresis, including the binary hysteresis of the Schmitt trigger, via single-valued descriptions; by choosing appropriate semi-state variables physical meaning can be ascribed to account for the jumps at different inputs following the philosophy of [2,p. 340].

Because of its interest for neural net-

works, we have developed a Schmitt trigger using a small number of CMOS transistors so that it may be realized via VLSI techniques. Here we describe this circuit, which is a four transistor device, with the design philosophy coming from semistate theory. Other MOS Schmitt triggers exist [11]-[19] some of which are also four transistor MOS circuits [12][13][16][19] though the characteristics are not as sharp as those obtained with the circuit presented here.

As background we review semistate theory in Section 2. In Section 3 we describe the circuit using semistate theory, where only single-valued functions are involved, and discuss how the circuit yields hysteresis, a multi-valued function. Section 3 also contains SPICE results and Section 4 has some discussion sion.

2. Brief Overview of Semistate Theory Semistate equations are generalizations of state variable equations which in canonical form are expressed as

$$E \cdot x' = A(x,t) + B \cdot u$$

(1a)

$y = C \cdot x$  (1b)

where x is the semistate vector, B, C, and E are constant matrices,  $A(\,\cdot\,,\,\cdot\,)$  is a nonlinear vector-valued function; u and y are the input and output, respectively and the prime 'denotes time, t, differentiation. A key feature of these equations is the possible singularity of E, which implies that nondynamic characteristics are included along with the dynamics of a system. In using (1) to describe systems the nondynamic, and the dynamic, characteristics will normally be single-valued functions in which  $A(\cdot,t)$  is a single-valued function. Equations (1) are known to be useful for describing hysteresis [10] even though hysteresis is described by multiple valued functionals. The presence of hysteresis is reflected in the semistate equations by double valued solutions of single-valued characteristics. In particular hysteresis results from the fact that there are multiple solutions of (1a) for the semistate x.

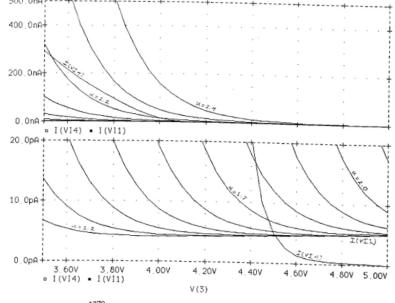

3. Circuit Description and Results Figure 1a shows our four transistor CMOS Schmitt trigger, and a typical DC hysteresis curve which results from it is seen in Fig. 1b. The circuit of Fig. 1a is a modification of the standard one presented in [14, Fig. 3] and has  $M_1-M_2$  forming a differential pair with  $M_3$  acting to steer the current between  $M_1$  &  $M_2$ .  $M_4$  acts as a load for the current of  $M_1$ across which the output voltage is taken (at node 3). Positive feedback to yield the hysteresis is achieved by attaching the gate of  $M_2$ , the second input of the differential pair, back to the drain of  $M_1$ , the first transistor in the differential pair to which the input voltage  $v_1 = u$  is applied.

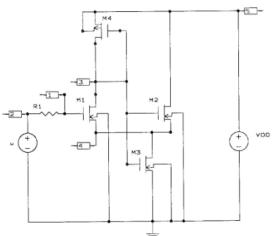

Figure 2 shows an equivalent circuit involving the key elements of interest for writing a semistate description of the circuit. Here we will choose the semistate the 5-vector, superscript T denoting Here we will choose the semistate to be transpose,

$$x = [v_1, v_3, i_{c1}, i_{cu}]^T$$

(2)

Using Kirchhoff's laws the resultant canonical semistate equations are readily found to be

<sup>\*</sup> Supported in part by NSF Grant MIP 87-19886

$$y = [.1.]x$$

(3b)

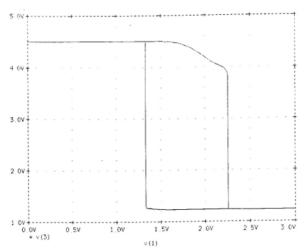

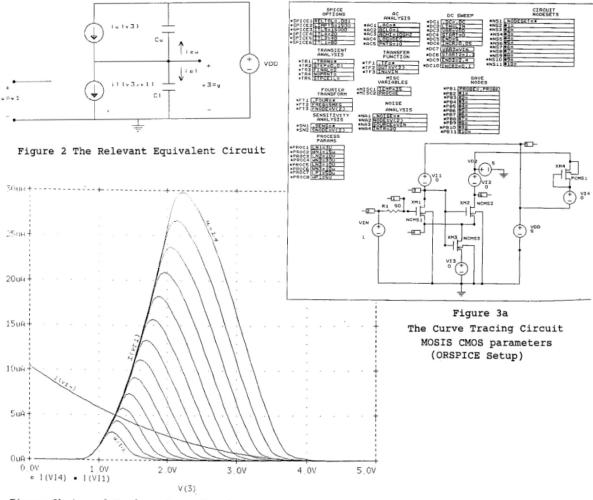

Here the upper current  $i_u$  is that through the diode connected load transistor  $M_4$  expressed as a function of the voltage  $v_3 = x_2$ ; that is  $i_u(x_2) = -i_d(v_3 - V_{DD})$  where  $i_d$  is the drain current taken as a function of the drain to source voltage. Similarly, the lower current  $i_1$  is that in the drain of  $M_1$  expressed as a function of  $v_3$  with  $x_1 = u = v_1$  as a parameter. Analytic expressions for these two currents,  $i_u$  and  $i_1$ , are possible but rather complex due to the number of regions traversed by the transistors. This is especially true for  $i_1$  since it incorporates the effects of  $M_1$ ,  $M_2$ , and  $M_3$ . However,  $i_1$  and  $i_u$  are relatively easily determined, once transistor parameters are known, via computer aided design packages, such as SPICE. Thus, using the curve tracing configuration of Fig. 3a run via ORSPICE (where the transistors receive a prefix X) with MOSIS CMOS parameters, a typical set of curves is graphed in Fig. 3b with an expanded view of these curves at large output voltages shown in Fig.3c. In this curve tracing  $i_u = I(VII4)$  is the current in  $M_4$  and  $i_1 = I(VII1)$  is the drain current of  $M_1$ , both being monitored in the zero voltage voltage sources similarly labelled; values including  $V_{DD} = 5$  are chosen to go with the hysteresis curve of Fig. 1b and  $u = v_1 = V(1)$  runs between 1.2v (the lower I(VII1) curve) and 2.4v (the upper I(VII1) curve) in 0.1 v steps.

Proceeding toward the hysteresis, we see from the third row of the semistate equations, (3a), that  $i_u=i_1$  at DC, i.e. when  $\mathbf{x}'=[0,0,0,0]^{\mathsf{T}}$ . That is, at DC the circuit has a solution when, by KCL, the upper current i equals the lower current i1. The curves for these two currents are single-valued when plotted versus v3, for a fixed input. However, they intersect at multiple points for certain values of the input, as again typicially seen in Fig. 3b, thus giving a multivalued input-output curve. This multivalued input-output curve is the hysteresis with the tracing remaining on a given branch (until switching is forced) due to the capacitors giving the dynamics in (3a). To see why switching occurs differently for increasing versus decreasing inputs, we can again consider Fig. 3 where we see that for small inputs there is no intersect point on the left (Fig. 3b) and only one on the right (lower curves of Fig. 3c). As the input is increased, the intersect point on the right remains but also a new one on the left comes about. For further increase in the input the one on the right actually disappears (after first branching into two), as seen in the expanded version of Fig. 3b shown in Fig. 3c; on disappearance, at about 2.24v, the only intersection is on the left and the system jumps to that intersection and remains there for further increases in the input. As the input is decreased the intersection on the left remains and is held as the solution well after the intersection on the right returns; a jump to the intersection on the right occurs when there is no more intersection on the left. The jump to the left intersection is seen to occur at a different value of the input than the jump to the right, giving rise to the hysteresis. As can be seen from Fig. 3c, there are some values of the input for which three intersections occur (but the intermediate intersection is not of practical interest for hysteresis, as it is undoubtedly unstable). From Fig. 3c it is also seen that the right most intersect point occurs for decreasing  $\mathbf{v}_3$ , as the input is increased, over part of the input range, this giving the dip in the hysteresis curve just before the full jump in the output from the high to the low level.

4. Discussion

Using semistate theory we have presented the idea behind the operation of our four transistor CMOS Schmitt trigger. This same idea can be developed for other transistor Schmitt triggers that occur in the literature, as referenced above. Possibly such developments could lead to improved insight of their operation, especially since some of the circuits behave differently when so viewed than the descriptions given in the literature for their operation. The advantage of the actual circuit presented here is its suitability for VLSI implementation, since only four readily integrated CMOS transistors are used. In preparing this study we also discovered another, actually very similar, four transistor Schmitt trigger with a layout given in a recently appearing VLSI text [19,plate 8]. In analyzing the circuit of [19], which earlier appears in [12, Fig. 1], we can set up i and i in a similar manner but one finds that both vary with the input if v3 is used as the common independent variable. Consequently, it is advantageous to switch to a different independent variable so that only one of the curves will vary with the input, with such a variable being v3-u.

being  $v_3$ -u. It should be noted that we could have given a larger set of semistate equations by including the current in  $M_2$  as well as by including the full descriptions of all of the tranistors. But for our purposes of describing the hysteresis all of these details are secondary and, hence, omitted in this short treatment.

From Fig. 3b it can be seen that if a larger hysteresis width is desired, then one wants to decrease the current through  $M_4$  which is readily done by decreasing its W/L ratio. However, an expression for the hysteresis width, as well as its center, are best developed via analytic expressions. Although an analytic expression for the upper current,  $i_{\rm u}$ , is readily given, one for the lower current,  $i_{\rm l}$ , is more complicated and still remains to be perfected.

References

[1] O. H. Schmitt, "A Thermionic Trigger," Journal of Scientific Instruments, Vol. 15, No. 1, January 1938, pp. 24 - 26. (see Fig. 1, p. 25, for a 2 triode, 5 resistor circuit)

[2] T. Kohonen, "Digital Circuits and Devices," Prentice-Hall, Englewood Cliffs, NJ, 1972.

[3] G. W. Hoffmann, "A Neural Network Model Based on the Analogy with the Immune

System, Journal of Theoretical Biology,

Volume 122, 1986, pp. 33-67.

[4] C. J. Savant, Jr., M. S. Roden, and

G. L. Carpenter, "Electronic Circuit Design,"

The Benjamin/Cummings Publishing Co., Menlo

Park, CA, 1987. [5] M. Shimura, [5] M. Shimura, "A Negative Hysteresis Threshold Circuit and Its Analysis," International Journal of Electronics, Vol. 34, No. 5, May 1973, pp. 641 - 653. (see Fig. 1 for a 4-triode, 8 resistor Schmitt trigger, the paper gives a mathematical analysis)

[6] E. J. Dickes and D. E. Carlton, "A Graphical analysis of the Schmitt Trigger Circuit," IEEE Journal of Solid-State Circuits, Vol. SC-17, No. 6, December 1982, pp. 1194

[7] C. J. F. Ridders, "Accurate Determination of Threshold Voltage Levels of a Schmitt Trigger," IEEE Transacions on Circuits and Systems, Vol. CAS-32, No. 9, September 1985, DD 269 - 270 (Tathernties) 1985, pp. 969 - 970. (mathematically analyzes a BJT circuit)

[8] S. C. Dutta Roy, "Comments on "Accurate Determination of Threshold Voltage Levels of a Schmitt Trigger," IEEE Transactions on Circuits and Systems, Vol. CAS-33, No. 7, July 1986, pp. 734 - 735. (mathematically analyzes a BJT circuit simplifying Ridders)

[9] H.-U. Lauer, "Comments on "Accurate

Determination of Threshold Voltage Levels of a Schmitt Trigger," IEEE Transactions on Circuits and Systems Vol. CAS-34, No. 10, October 1987, pp. 1252 - 1253. (improves upon ber 1987, pp. 1252 - 1253. (improve Dutta Roy's results) [10] R. W. Newcomb and B. Dziurla,

[10] R. W. Newcomb and B. Dziurla, "Some Circuits and Systems Applications of Semistate Theory," Circuits Systems and Signal Processing, Vol. 8, No. 3, 1989, pp. 235 - 260.

[11] A. A. Abidi and R. G. Meyer, "Noise in Relaxation Oscillators", IEEE Journal of Solid-State Circuits, Vol. SC-18, No. 6, December 1983, pp. 794 - 802. (see Fig. 18 of Appedix 1 for a 2 transistor, 2 resistor, current source and gain stage Schmitt trigger)

Figure 1a The Circuit

[12] B. L. Dokić, "CMOS Schmitt Triggers," IEE Proceedings, Vol. 131, Part G, No. 5, October 1984, pp. 197 - 202. (see Fig. 1, p. 197, for a 4 transistor CMOS circuit and Fig. 6, p. 200 for an improved 6 transistor

[13] L. A. Glasser and D. W. Dobberpuhl, "The Design and Analysis of VLSI Circuits,

The Design and Analysis of VLSI Circuits," Addison-Wesley Publishing Co., Reading, MA, 1985. (see Fig. 5.40, p. 281, for a 6 transistor CMOS and a 4 transistor nMOS circuit) [14] M. J. S. Smith, "On the Circuit Analysis of the Schmitt Trigger," IEEE Journal of Solid-State Circuits, Vol. 23, No. 1, February 1988, pp. 292 - 294. (see Fig. 3 for a 2 transistor, 1 resistor, 1 current source MOS sistor, 1 resistor, 1 current source MOS Schmitt trigger from which ours has evolved)

[15] D. A. Hodges and H. G. Jackson,

"Analysis and Design of Digital Integrated

Circuits," Second Edition, McGraw-Hill Book

Co., NY, 1988. (see Fig. 8.23, p. 321 for a 12

transistor CMOS circuit and Fig. 8.23, p. 321 for a 12 transistor CMOS circuit and Fig. 8.21, p. 318 for an emitter coupled BJT circuit)

[16] J. P. Uyemura, "Fundamental of MOS Digital Integrated Circuits," Addison-Wesley Publishing Co., Reading, MA, 1988. (see Fig. 7.15, p. 401 for a 4 transistor nMOS and Fig. 7.31, p. 422, for a 6 transistor CMOS)

7.31, p. 402 for a 4 transistor nMoS and Fig.

7.31, p. 422, for a 6 transistor CMOS)

[17] Z. Wang and W. Guggenbuehl, "Novel

CMOS Current Schmitt Trigger," Electronics

Letters, Vol. 24, No. 24, November 24, 1988,

pp. 1514 - 1516. (uses 7 transistors + 2 current sources) rent sources)

Wang and W. Guggenbuehl, "CMOS [18] Z. Current Schmitt Trigger with Fully Adjustable Hysteresis," Electronics Letters, Vol. 25, No. Hysteresis," Electronics Letters, Vol. 25, No. 6, March 16, 1989, pp. 397 - 398. (uses 8 transistors + 3 current sources)

[19] R. L. Geiger, P. E. Allen, and N. R. Strader, "VLSI Design Techniques for Analog and Digital Circuits," McGraw-Hill Publishing NY, 1990. (see Plate 8 for the layout of the Schmitt trigger of Fig. 1 of Dokic)

Figure 1b Resulting Hysteresis

Figure 3b  $i_{\text{u}}$  and  $I_{\text{1}}$  from Curve Tracing

Figure 3c Two Expansions

$\mbox{ of } \textbf{i}_{\textbf{u}} \mbox{ and } \textbf{i}_{\textbf{1}}$  Near Upper Hysteresis Level