Multilevel Neural-Type Lattices\*

Nevine El-Leithy\*, Robert W. Newcomb\*+, Tuni Aldave+, Victoria Rodellar+, & Pedro Gómez+

\* Microsystems Laboratory, Electrical Engineering Department University of Manufact Detrical Engineering Department

University of Maryland, College Park, MD 20742 USA + Grupo de Trabajo en Sistemas (PARCOR), Departemento de Electrónica, Facultad de Informática, Ctra. de Valencia, Km. 7,00, 28031 Madrid, Spain

#### Abstract

Ting to and

A multilevel neural-type logic lattice is introduced following the original description of Toda. Electronic circuits for this Toda lattice are developed and CAD results presented on the soliton type of pulses it handles. Circuits are also discussed for realizing a modification of the previously introduced neural-type logic lattices.

## I. Introduction

Previously multilevel neural-type logic lattices were introduced which work on the soliton principle [1]. In these information is carried on pulses that travel in the system with pulses of different heights traveling at different velocities and not interfering with each other. Electronic circuit realizations of the circuits of [1] require analog multipliers, which though possible for construction in integrated circuit form, are somewhat inconvenient. Consequently, we look here at another class of solitons [2], those from which the equations in [1] are actually transformed. These more fundamental equations have for thier nonlinearity an exponential, rather than a product, and as such should be more amenable to integrated circuit constructions since one can realize the exponentíals vía solid-state diodes.

```

II. The Basic System

```

The basic theory for our circuits is found in [2], an early paper (1967) by Toda where he first presents what has come to be known as the Toda lattice [3, Chap. 7]. In [2] Toda considers a uniform chain of particles with an exponential interaciton energy between adjacent particles. Fut into state-variable form his equations (2.10) and (3.3) are, respectively,

| mdr_/dt             | = | 25n - 5n-1 - 5n+1 | (1a) |

|---------------------|---|-------------------|------|

| ds <sub>n</sub> /dt | = | -a(1-exp(-br_))   | (16) |

\* Research supported in part by the US-Spain Joint Commission under Grant CCB-84-02002 and for the first two authors also under the US National Science Foundation under Grant ECS 85-06924. Here a, b, m are positive constants. With normalized mass, m=1, and driven by intial conditions, these are shown to have the solutions (equations (3.12) & (3.6) of [2])

| rn = (-1/b) •<br>ln(1+(2Κμ)²[dn²{2Κ(μt+(n/λ)}-(Ε/Κ | )]/ab)                |

|----------------------------------------------------|-----------------------|

| $s_n = (2Kb/\nu)Z\{2K(\nu t + (n/\lambda))\}$      | (2 <b>a</b> )<br>(2b) |

where

# $2K\nu = [ab/{(sn^2(2K/\lambda))^{-1}-1+(E/K)]^{1/2}}$ (2c)

and sn, dn and Z are Jacobian elliptic functions, which, along with K, are functions of the modulus k and tabulated in terms of  $m=k^2$  [4]. There are actually two solutions, a right traveling one and a left traveling one; we have arbitrarily chosen the left traveling one and obtain circuit realizations for it.

Of interest to us is the fact that the exponential term in (1b) is similar to the solid-state diode characterization [5, p. 142]

$$\mathbf{i} = -\mathbf{I}_{\bullet}\{1 - \exp(\mathbf{v}/\mathbf{V}_{\mathbf{T}})\}$$

(3)

where the saturation current, I<sub>s</sub>, and the thermal voltage,  $V_{\tau}$ , are constants dependent upon temperature. Thus, the Toda lattice of equations (1) should have a nice realization in terms of electronic circuits where the nonlinearity is obtained simply through the use of diodes. However, in realizing (1b) via an integration one runs into a difficulty in that the charge on the integrator simply accumulates due to the diode rectification action. Consequently, it is expeditious to introduce a new difference variable

$Y_n = S_n - S_{n-1} \tag{4a}$

Equations (1) are then rewritten as

$$\frac{mdr_{n}/dt}{dy_{n}/dt} = \frac{y_{n} - y_{n+1}}{(4c)}$$

-a{1-exp(-br\_)}+a{1-exp(-br\_\_\_)}

We do note that we could have chosen  $s_{n+1}$  as the second term in defining  $y_n$ ; this has the effect of changing left going pulses into right going ones.

Toward an actual realization we first perform some normalizations. For this we multiply (4b) by  $\alpha$ , (4c) by  $\beta$ , and let s=d/dt to get

$$\begin{array}{ll} \alpha r_n &= -(\alpha/m\beta s) [\beta y_{n+1} &= \beta y_n] & (5a) \\ \beta y_n &= -(a\beta/s) [(exp(-(b/\alpha)(\alpha r_{n-1}))-1) \\ &\quad -\{exp(-(b/\alpha)(\alpha r_n)-1\}] \end{array}$$

(5b) It is, therefore, convenient to let

$$\ddot{R}_n = \alpha r_n$$

(5c)

$Y_n = \beta y_n$  (5d)

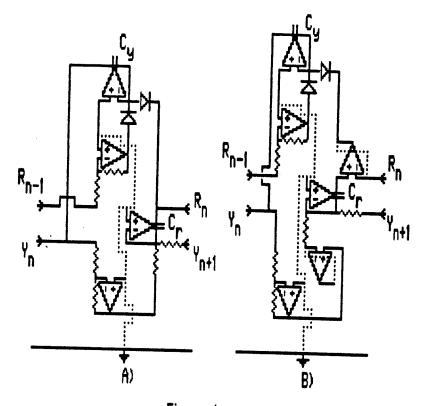

Realizing the exponentials via the diodes of (3), Fig. 1A) shows a circuit realization of the nth lattice section of this Toda lattice where we see that

| ∨ <sub>▼</sub> | - | α/b                | (6a) |

|----------------|---|--------------------|------|

| C, R           | × | mβ/α               | (6b) |

| C,             | # | I <sub>m</sub> /aβ | (6c) |

Figure 1B) is identical to Fig. 1A) except that two isolation amplifiers are introduced to break some loops that could change the characteristics of the circuit. However, we found very little difference in performance between the two types of sections, and, hence, used Fig. 1A) for the simulations presented below. We then can make the following choices

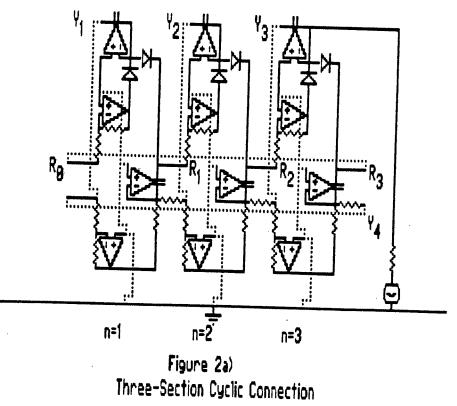

which give  $\alpha = V_{T}$ ,  $\beta = 1E-4$ . Here we have chosen  $V_{T} = (1E-2)/4$  for numerical convenience. Using these values a cyclic three section system was simulated using MICROCAP on an IBM FC, the circuit diagram being as shown in Fig. 2a); Fig. 2b) contains a NET-LIST of node numberings for the connections. For this cyclic connection the mth and nth lattice sections are related by

$$n \equiv m \operatorname{Mod}(3) \tag{8}$$

while the problem of loading is avoided since each section sees another to its right and left. However, since MICROCAP would not proceed with this circuit excited by other than zero initial conditions, it was necessary to insert an external source, this being inserted on the right to charge  $C_{\gamma}$  to give a positive Y<sub>3</sub>. The pulse chosen is listed as V(t) in the NETLIST (item 44). Two different peak values were chosen to show the speedup of higher amplitude pulses. Among the effects of this external source is to put a bias on  $Y_n$  in which case a very short pulse was used so that the circuit responses are not unduly disturbed; but a theoretical analysis remains to be made on its mathematical effects. Indeed it

is not clear yet as to how the resulting pulses are related to the soliton solutions given above in terms of Jacobian elliptic functions.

Refering to Fig. 1 the operation of a section can be described as follows. Consider that at a given instant  $Y_n$  is positive. This tends to make  $R_{n-1}$  negative, via the presence of Yn on the (n-1)st section Cr integrator, which in turn forward biases the left hand nth section diode causing Yn to decrease. R<sub>n-1</sub> negative also forward biases the right hand diode of the (n-1)st section causing  $Y_{n-1}$  to go positive in which case the pulse travels to the left. The larger  $Y_n$  is the faster the (n-1)st section C<sub>r</sub> accumulates charge causing Y<sub>n</sub> to decrease faster (via the left hand oth section diode), in which case the pulse travels faster. At this point we can also see the effect of the alternate choice for yn Imade by choosing  $s_{n+1}$  as the second term on the right of (4a)]; a circuit based on this choice in essence reverses the right and left sides of Fig. 1, or with the labeling of Fig. 1 has pulses traveling to the right.

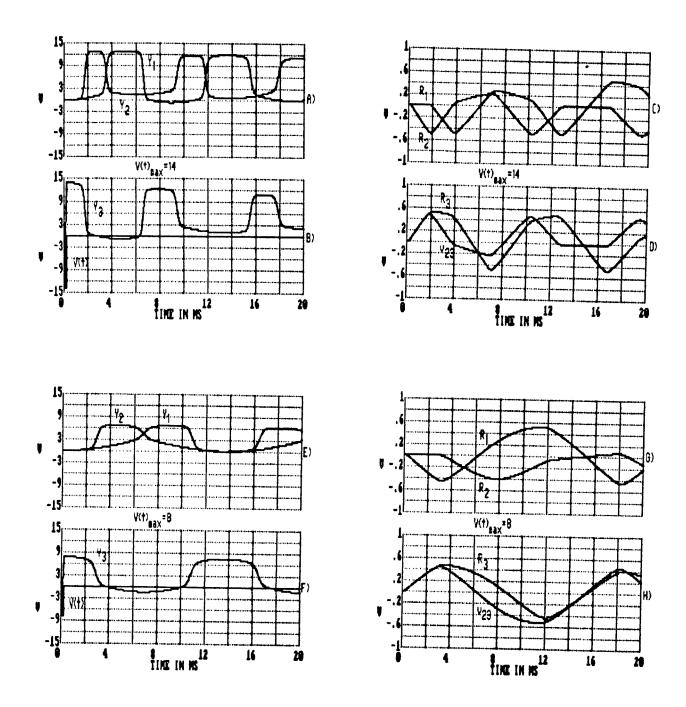

Typical results of the simulation are shown in Fig. 3, where the pulse shaping and propagating properties are shown. The signals  $Y_1$ ,  $Y_2$ ,  $Y_3$ , input pulse v(t),  $R_1$ ,  $R_2$ ,  $R_3$ , and diode voltage  $v_{29}$  are shown in the figure for two different peak values of the input pulse (14 & 8 volts respectively). One sees that in time sequence  $Y_{a}$ first forms and then it transfers to  $Y_{2}$  and then to Y1. Comparing the upper four portions of the figure with the lower four portions one sees that there is a higher velocity of propagation with the higher peaked pulses. Unfortunately, MICROCAP does not allow us to extend the response much further in time so in the future it is necessary to either simulate with a more substantial program or, better yet, to build the circuit and make real time measurements.

Once having established the feasibility of this Toda lattice realization it is next important to obtain simplified circuits. Toward that we note the very nice differential pair integrator presented in [6, Fig.5] which it seems could be used to simplify the integrator portions of the circuit.

III. Froduct Realization

In [1] the soliton implementations were proposed through the lattice equations

$$df_n/dt = b_n - b_{n+1}$$

(9a)

$$db_n/dt = (f_{n-1} - f_n)(b_n + 1)$$

(9b)

Since the last term necessitates insertion of a bias into the circuits, it may prove more useful to let

$$F_n = f_n, \quad B_n = b_n + 1 \quad (9c)$$

to get the equations in the form

$$dF_{n}/dt = B_{n} - B_{n+1}$$

(10a)

$$dB_{n}/dt = B_{n}(F_{n-1} - F_{n})$$

(10b)

It appears that the product of (10b) can be realized as part of the differential integrator mentioned above [6] where the current sources biasing the circuit can be made proportional to  $B_n$ , this following one of the standard ways of making multipliers [7, p.605]. Since the right hand sides of both (10a) and (10b) have difference signals to be integrated, they could then be conveniently realized by the differential integrator, though one would need to switch between appropriately level shifted structures to maintain the system bias levels.

### IV. Discussion

Here we have presented a circuit for the Toda lattice in a form suitable for integrated circuit realization. To do this we have used solid-state diodes to realize the nonlinearities needed in any soliton system. However, for each section we have used two diodes where actually one should suffice, and, thus, we see that there is room for improvement in the circuits realized. For any use as logic elements in a neural-type computer it is of course important to have circuits that can be constructed conveniently in integrated circuit form because of the very large numbers of lattice sections that would be required.

It should be noted that this "Toda lattice" is not a lattice of the kind known as a lattice in the circuit theory and/or digital filtering fields, the term lattice having more the meaning of lattice in the a crystal lattice. However, these Toda lattices have been realized in the literature via the ladder structures of circuit theory [8][9]. Because of their possibility of avoiding the use of op-amps to realize the connection constraints of the Toda lattice equations, ladder structures are attractive. However, the ones in the literature are really not practical for integrated circuits since they rely on the use of inductors and the nonlinearity of junction capacitors (which in itself is not of the directly desired logarithmic form). Further, something like 46 sections are needed to develop the soliton pulses [9, p.682]. But by the use of gyrators for inductor replacement and use of diodes for the exponential nonlinearities it may be possible to obtain nice ladder structures; it is certainly worth further investigation.

One of the bigger problems still to be faced in making these structures practical is how to conveniently form the soliton pulses and how to inject them into the circuits. The means used here of injecting a short sharp pulse is convenient but it remains to see how many travels through the cyclic structure are needed until it is formed into any kind of soliton as well as how to accomodate the dc bias that it inserts into the traveling pulses.

The use of differnial integrators appears to make practical the Toda lattice realized by products, as in (10) above. This aspect of the topic area also needs to be further developed and constructions carried out.

### References

[1]. R. W. Newcomb, V. Rodellar, and P. Gómez, "A Nonlinear Lattice for Multivalued Neural-Type Logic," Proceedings of the 1985 IEEE Workshop on Languages for Automation, Palma de Mallorca, Spain, June 28, 1985, pp. 44-46.

[2]. M. Toda, "Vibration of a Chain with Nonlinear Interaction," <u>Journal of the</u> <u>Physical Society of Japan</u>, Vol. 22, No. 2, February, 1967, pp. 431-436.

[3]. G. Eilenberger, "Solitons," Springer-Verlag, Berlin, 1981.

[4]. L. M. Milne-Thomson, "Jacobian Elliptic Function Tables," Dover Publications, New York, 1950.

[5]. D. A. Hodges & R. G. Jackson, "Analysis and Design of Digital Integrated Circuits," McGraw-Hill Book Co., New York, 1983.

[6]. H. Khorramabadi & P. R. Gray, "High-Frequency CMDS Continuous-Tiem Filters," <u>IEEE Journal of Solid-State Cir-</u> <u>cuits</u>, Vol. SC-19, No. 6, December 1984, pp. 939-948.

[7]. J. Millman, "Microelectronics," McGraw-Hill Book Co., New York, 1979.

[8]. R. Hirota & K. Suzuki," Theoretical and Experimental Studies of Lattice Solitons in Nonlinear Lumped Networks," <u>Proceedings of the IEEE</u>, Vol. 61, No. 10, October 1973, pp. 1483-1491.

[9]. H. Nagashima & Y. Amagishi, "Experiments on the Toda Lattice Using Nonlinear Transmission Lines," Journal of the <u>Physical Society of Japan</u>, Vol. 45, No. 2, August 1978, pp. 680-688.

Figure 1 nth Section of Toda Lattice Circuit

×

|      |           |      |      |      |    | Figure 2<br>NETLIST |       |     |               |                 |         |       |       |      |       |      |     |       |

|------|-----------|------|------|------|----|---------------------|-------|-----|---------------|-----------------|---------|-------|-------|------|-------|------|-----|-------|

|      |           |      |      |      |    | TLATSTO2 EI         |       |     |               |                 |         |       |       |      |       |      |     |       |

| REF  | COMPONENT | 00   | NNEC | TION | IS | PARAMETER           |       |     |               |                 |         |       |       |      | ,     |      |     |       |

|      |           | 11   |      | 00   | T  | OR                  |       |     |               |                 |         |       |       |      |       |      |     |       |

| HO.  | MAKE      | -    | +    | -    | +  | TYPE                |       |     |               |                 |         |       |       |      |       |      |     |       |

| 1    | CAPACITOR | 9    | 24   | 0    | 0  | 1E-10               |       |     |               |                 |         |       |       |      |       |      |     |       |

| 2    | OPAMP     | 24   | 0    | 0    | 9  | 6 RI=               | 1E+08 | A0= | 20000         | )0 RD=          | 10000   | VOFF* | .000  | 001  | VMA1= | 30   | C0= | 0     |

| 3    | CAPACITOR | 11   | 25   | 0    | 0  | 1E-10               |       |     |               |                 |         |       |       |      |       |      |     |       |

| 4    | OPANP     | 25   | 0    | 0    | 11 | 6 RI=               | 1E+08 | AD= | 20000         | XX RD=          | 10000   | VOFF= | .000  | 001  | VNA1= | 30   | C0= | 0     |

| 5    | CAPACITOR | 13   | 0    | 0    | 0  | 1E-10               |       |     |               |                 |         |       |       |      |       |      |     |       |

| 6    | DPAMP     | 8    | 0    | 0    | 13 | 6 RI=               | 1E+08 | A0= | 20000         | )0 RO=          | 10000   | VOFF= | .000  | 001  | VNAX= | 30   | C0* | 0     |

| 7    | DIODE     | 16   | 24   | 0    | 0  | 6 10×               | 1E-14 | ¥Z= | 200           | RZ= 10          | RF= 1   | VT=   | . 025 | RP*  | 1E+07 |      |     |       |

| 8    | DIDDE     | 24   | 19   | 0    | 0  | 6 10=               | 1E-14 | ¥Z≠ | 200           | RZ= 10          | RF= 1   | ¥7=   | .025  | RP×  | 1E+07 |      |     |       |

| 9    | DIODE     | 17   | 25   | 0    | 0  | 6 10=               | 1E-14 | ¥Z× | 200           | RZ= 10          | RF= 1   | ¥T*   | .025  | R₽≠  | 1E+07 |      |     |       |

| 10   | DIODE     | 25   | 21   | 0    | 0  | 6 IO=               | 1E-14 | ¥Z≖ | 200           | RZ= 10          | RF= 1   | ¥T*   | . 025 | RP=  | IE+07 |      |     |       |

| 11   | DIODE     | 15   | 8    | 0    | 0  | 6 10=               | 1E-14 | ٧Z= | 200           | RZ= 10          | RF= 1   | V⊺≖   | . 025 | RP*  | 1E+07 |      |     |       |

| 12   | DIODE     | 8    | 23   | 0    | 0  | 6 10=               | 1E-14 | VZ= | 200           | RZ= 10          | RF= 1   | VŢ≖   | . 025 | RP=  | 1E+07 |      |     |       |

| 13   | OPAMP     | 18   | 0    | 0    | 19 | 6 R1=               | 1E+08 | A0= | 2000          | 00 RO=          | 10000   | VOFF= | .000  | 001  | VMAX= | 30   | C0= | 0     |

| 14   | RESISTOR  | 18   | 19   | 0    | 0  | 1E6                 |       |     |               |                 |         |       |       |      |       |      |     |       |

| 15   | RESISTOR  | 18   | 15   | 0    | 0  | 1E6                 |       |     |               |                 |         |       |       |      |       |      |     |       |

| 16   | OPAMP     | 20   | 0    | 0    | 21 | 6 RI=               | 1E+08 | AO= | 2000          | 00 RO=          | 10000   | VOFF= | .000  | 001  | VNAI= | 30   | C0= | 0     |

| 17   | RESISTOR  | 20   | 21   | 0    | 0  | 1E6                 |       |     |               |                 |         |       |       |      |       |      |     |       |

| 18   | RESISTOR  | 20   | 16   | 0    | 0  | 1E6                 |       |     |               |                 |         |       |       |      |       |      |     |       |

| 19   | OPAMP     | 22   | 0    | 0    | 23 | 6 R1=               | 1E+08 | AO= | 2000          | 00 RD=          | 10000   | VOFF= | .000  | 001  | VMAI= | 30   | C0= | 0     |

| 20   | RESISTOR  | 22   | 23   | 0    | 0  | 1E6                 |       |     |               |                 |         |       |       |      |       |      |     |       |

| 21   | RESISTOR  | 22   | 17   | 0    | 0  | 1E6                 |       |     |               |                 |         |       |       |      |       |      |     |       |

| 22   | CAPACITOR | 16   | 10   | 0    | 0  | 4E-8                |       |     |               |                 |         |       |       |      |       |      |     |       |

| 23   | OPANP     | 10   | 0    | 0    | 16 | 6 RI×               | 1E+08 | A0= | 2000          | 00 RO=          | 10000   | VOFF= | .000  | 001  | VMAX= | 30   | CO= | 0     |

| 24   | RESISTOR  | 10   | 11   | 0    | 0  | 1E6                 |       |     |               |                 |         |       |       |      |       |      |     |       |

| 25   | RESISTOR  | 10   | 1    | 0    | 0  | 1E6                 |       |     |               |                 |         |       |       |      |       |      |     |       |

| 26   | CAPACITOR | 17   | 12   | 0    | 0  | 4E-8                |       |     |               |                 |         |       |       |      |       |      |     |       |

| 27   | OPANP     | 12   | 0    | 0    | 17 | 6 RI=               | 1E+08 | A0= | 2000          | 0 <b>0 RD</b> = | 10000   | VOFF= | .000  | 001  | VNAX= | 30   | C0* | 0     |

| 28   | RESISTOR  | 12   | 13   | 0    | 0  | 1 E 6               |       |     |               |                 |         |       |       |      |       |      |     |       |

| 29   | RESISTOR  | 12   | 2    | 0    | 0  | 1E6                 |       |     |               |                 |         |       |       |      |       |      |     |       |

| 30   | CAPACITOR | 15   | -14  | 0    | 0  | 4E-8                |       |     |               |                 |         |       |       |      |       |      |     |       |

| 31   | DPAMP     | - 14 | 0    | 0    | 15 | 6 RI=               | 1E+08 | A0= | 2000          | 00 <b>RD</b> =  | 10000   | VOFF= | .000  | 001  | VMAI= | 30   | C0= | 0     |

| 32   | RESISTOR  | - 14 | 9    | 0    | 0  | 1E6                 |       |     |               |                 |         |       |       |      |       |      |     |       |

| 33   | RESISTOR  | - 14 | 3    | 0    | 0  | 1E6                 |       |     |               |                 |         |       |       |      |       |      |     |       |

| - 34 | DPANP     | 5    | 0    | 0    | 1  | 6 RI=               | 1E+08 | A0= | 2000          | 00 RO=          | 10000   | VOFF= | .000  | 001  | VMAX= | 30   | C0* | 0     |

| 35   | RESISTOR  | 9    | 5    | 0    | 0  | 1E6                 |       |     |               |                 |         |       |       |      |       |      |     |       |

| 36   | RESISTOR  | 5    | 1    | 0    | 0  | 1E6                 |       |     |               |                 |         |       |       |      |       |      |     |       |

| 37   | OPAMP     | 6    | 0    | 0    | 2  | 6 RI=               | 1E+08 | AD= | 2000          | 00 <b>RO</b> =  | 10000   | VOFF× | .000  | 001  | VNAX= | 30   | C0× | 0     |

| 36   | RESISTOR  | 11   | 6    | 0    | 0  | 1E6                 |       |     |               |                 |         |       |       |      |       |      |     |       |

| 39   | RESISTOR  | 6    | 2    | 0    | 0  | 1E6                 |       |     |               |                 |         |       |       |      |       |      |     |       |

| 40   | OPANP     | 7    | 0    | 0    | 3  | 6 R1=               | 1E+08 | AO= | 2000          | 00 RO=          | 10000   | VOFF= | .000  | 001  | VMAX= | 30   | C0= | 0     |

| 41   | RESISTOR  | 13   | 7    | 0    | 0  | 1E6                 |       |     |               |                 |         |       | \$    |      |       |      |     |       |

| 42   | RESISTOR  | 7    | 3    | Û    | 0  | 1E6                 |       |     |               |                 |         |       |       |      |       |      |     |       |

| 43   | RESISTOR  | 8    | 4    | 0    | 0  | 1E6                 |       |     |               |                 |         |       |       |      |       |      |     |       |

| - 14 | V(T)      | 4    | 0    | 0    | 0  | 6 PO=               | 0 P1  | • 0 | ₽2 <b>=</b> . | 0001 P          | 3= .000 | 101 P | 4= .0 | 0019 | 9 P5= | . 00 | 02  | P6= : |

$1 \leq 2$

•

.

. .

**:**--

.

Figure 3 Typical Responses

matern System Design

NATIONAL UNIVERSITY OF SINGAPORE KENT RIDGE, SINGAPORE AUGUST 27-29, 1986

Sponsors Case Western Reserve University, Illinois Institute of Technology, Institute of Systems Science (National University of Singapore)

In cooperation with IBM Singapore PIELId: Sperry PIELId. Texas Instruments Singapore PIELId: IEEE computer Society Order Number 7251 Ubrary of Congress Number 85 (45863) IEEE Catalog Number 86 (10158-6) ISBN 0-8186-0725-4