A Nonlinear Lattice for Multivalued Neural-Type Logic\*

R. W. Newcomb\*\* - V. Rodellar - P. Gomez

Grupo de Trabajo en Systemas PARCOR - Departamento de Electronica Facultad de Informatica - Universidad Politecnica de Madrid Etra. de Valencia, Km. 7,00 - 28031 Madrid - Spain

## ABSTRACT:

.

A nonlinear lattice structure is introduced for the processing of multivalued neural-type pulses. This is based upon the Toda lattice of soliton theory and gives pulse propagation speed proportional to the amplitude of the pulse being processed.

#### INTRODUCTION

Our development begins with the concept of solitons which in turn are special cases of solitary pulse waves. Solitary pulses are pulses that propagate in a medium without changing form, neural action potential pulses being of this form. Solitons are special solitary pulses that on collision pass through each other without change. Although solitons in the form of water waves have been of scientific interest since at least the 1840's [1], only recently have extensive studies been undertaken. A surprising number of media support solitons and at this point the theories have developed to the extent that a number of books are emerging from the research literature [2] [3]. Among the structures yielding solitons, of special interest to us is the Toda lattice which was developed by Toda beginning in the early 1960's and which is discussed in detail in Toda's book [4] which will be our primary reference for this paper.

\*Research supported in part by the US Spain Joint Commission uder Grant CCB-84-902 and for the first author also in part by the US National Science Foundation under Grant ECS 83-17877.

\*\*On leave from Microsystems Laboratory, Flectrical Engineering Department, University of Maryland, College Park, MD 20742 USA.

Here in the next section we discuss the basic Toda lattice followed by a section on an alternate more suitable for microelctronic circuit realization. Following that a brief discussion is given on the use of the lattice in multiprocessor computing. The final section is devoted to a brief mention of open problems.

#### Toda Lattice

By the <u>Toda Lattice</u> we mean the cascade of lumped cells where the nth cell has the description [4, p. 125]

$$dq_n/dt = p_n \tag{1a}$$

$$dp_n/dt = exp(-\{q_n-q_{n-1}\}) - exp(-\{q_{n+1}-q_n\})$$

(1b)

Toda was led to these equations through the interaction of masses with exponential potential functions. Setting

$$r_0 = q_0 - q_{0-1}$$

(2)

he was led to the soliton solutions [4, p.23]

$$\exp(-r_n) - 1 = \beta^2 \operatorname{sech}^2(\alpha n \pm \beta t)$$

(3a)

with

$$\theta = \sinh(\alpha)$$

(3b)

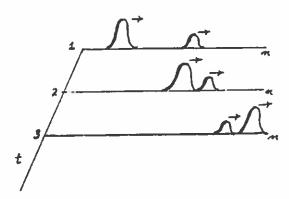

Then, choosing the lattice spacing as normalized unit length, the speed of the soliton pulse is  $\beta/\alpha$ . Since  $\beta^2$  is the amplitude of the soliton pulse, we see that the speed of propagation and the the amplitude of the soliton are each uniquely determined by the other and both are fixed by the parameter  $\alpha$ . Of considerable interest is the fact that this lattice supports more than one traveling (soliton) pulse and that these solitary waves indeed do pass right through each other [4, pp. 25-28]. According to the speed property just cited, if two solitons are travelling in the same direction the larger one will eventually overtake the smaller one, as

shown in Fig.1 (where the curves are drawn for noninteger n to indicate the pulse progress). Using nonlinear LC transmission lines these solitons have been simulated via electrical circuits [5]. But such simulations have required capacitors with logarithmic variation of the capacitance with voltage, and, hence, are impractical for microelctronic realization of soliton circuits.

# IMPLEMENTABLE LATTICES

Implementation of (1) requires the use of exponential nonlinearities in a rather awkward form for microelectronic constructions. Consequently, we make a change of variables which will lead to product nonlinearities rather than exponential ones. Thus, let

$$f_n = p_n$$

(4a)

$$b_n = \exp(-r_n) - 1$$

(4b)

=  $\exp(-(q_n - q_{n-1})) - 1$

where (4b) is chosen because of (3a) and the symbolism is such that for means forward (wave) input to the (n+1)st cell and bo means backward (wave) output of the nth cell. In the notation of (4) equations (1) become

$$df_{D}/dt = b_{D} - b_{D+1} \tag{5a}$$

$$db_0/dt = (f_{n-1} - f_n)(b_n + 1)$$

(5b)

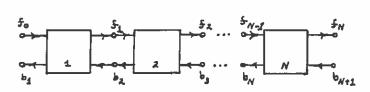

A system represented by (5) we shall also call a Toda lattice. Figure 2 shows a symbolic representation of a Toda lattice of N such cells. Following (3) single soliton solutions of these Toda lattice equations are

$$fn(t) = \pm g[\tanh(\alpha n \pm gt) - \tanh(\alpha(n+1) \pm gt)]$$

(6a)

$$bn(t) = \beta^2 sech^2 \{\alpha [n \pm (\beta/\alpha)t]\}$$

(6b)

speed =

$$[sinh(\alpha)]/\alpha$$

(6c)

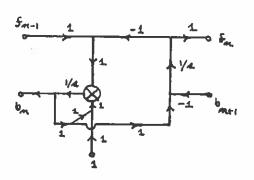

Using 1/s for integration Fig. 3 gives a signal flow graph of equations (5) showing that each cell can be realized with the nonlinearity being at most one multiplication. Since both integrators and multipliers are possible integrated circuit devices [6], these cells are amenable to microelectronic construction. A point of considerable practical importance for finite length Toda lattices is the fact that to support the soliton an excitation that is of the form of (6) is needed.

It should be noted that an alternate cell is given by Toda [4, p. 125] using the change of variables

$$2a_n = \exp[(-r_{n+1})/2] \tag{7a}$$

$$2b_{n} = p_{n}$$

(7b) and yielding

$$da_n/dt = a_n(b_n - b_{n+1})$$

(7c)

$db_n/dt = 2(a_{n+1}^2 - a_n^2)$  (7d)

However, a cell built on these latter equations requires two multipliers per cell and is, hence, much less convenient than a cell built upon (5).

## COMPUTER USE

Since solitons are solitary waves they have many of the essential properties of neural pulses. Thus, much of the theory and background that is built up around neural-type computer systems [7], [8] is applicable. Primarily lacking are the refractory period properties, though separate refractory period cells could be introduced if needed. However, the refractory period property does not appear to be needed as indicated by the two different neuristor logic systems of Wilamowski [9] and Gutierrez [10]. For example neuristor ring storage configurations can be constructed using the lattices discussed here by connecting the left terminals to the right ones in Fig. 2, that is by setting  $f_0 = f_N$  and  $b_{N+1} = b_1$ , and introducing signals on any forward lead as an input. One can modulate the pulse repetition rate separately for each amplitude, and, through that process (and following the ideas of Gutierrez [10]), it seems very possible to make a processor that simultaneously handles many jobs. The number of jobs would be equal to the number of pulse amplitude values allocated, that is, to the number of possible pulse amplitudes one would allow in the system. For this one would set preassigned amplitudes as standard. separating these magnitudes sufficiently to allow for tolerances of the signals and components such that normal noise would not allow two different amplitudes to be confused as being equal.

## DISCUSSION

We have introduced a system that seems to hold considerable promise for multiprocessing computers. But the ideas are really only initiated here and more questions are raised than answered or for which we even have room to mention. Among these is the question of initiating soliton pulses for which new oscillators need to be conceived, as well as the tolerances allowed in a signal in order that it can proceed in the system as a soliton wave. The cells discussed here require multipliers, a component that is not very desirable even though it is possible to be constructed. Perhaps some further modification in the basic cell equations will allow a simpler construction using diodes to realize the exponentials of (1b). Further, perhaps the integrators can be replaced by delays in which case much more conventient structures could be realized.

Finally we point out that the Toda lattice cells discussed here are naturals for systolic arrays and, hence, any computer constructed from them should have all the advantages of systolic array processors [11].

REFERENCES

- [1] A. C. Scott, F. Y. F. Chu, and D. W.

McLaughlin, "The Soliton: A New Concept

in Applied Science," Proceedings of the

IEEE, Vol. 61, No. 10, October 1973,

pp. 1443 1483.

- [2] G. Eilenberger, "Solitons,"

Springer-Verlag, Berlin, 1981.

١.

- [3] R. K. Bullough and P. J. Caudrey, Editors, "Solitons," Springer-Verlag, Berlin, 1980.

- [43 M. Toda, "Theory of Nonlinear Lattices," Springer-Verlag, Berlin, 1981.

- [5] R. Hirota and K. Suzuki, "Theoretical and Experimental Studies of Lattice Solitons in Nonlinear Lumped Networks," <u>Proceedings of the IEEE</u>, Vol. 61, No. 10, October 1973, pp. 1483 - 1491.

- [6] M. Herpy, "Analog Integrated Circuits," John Wiley & Sons, New York, NY, 1980.

- NY, 1980.

[7] H. D. Crane, "Neuristor A Novel

Device and System Concept," Proceedings

of the IRE, Vol. 50, No. 10, October,

1962, pp. 2048 2060.

- 1762, pp. 2048 2060.

[8] R. W. Newcomb, "MOS Neuristor Lines," in Constructive Approaches to Mathematical Models, Edited by C. V. Coffman and G. J. Fix, Academic Press, NY, 1979, pp. 87 111.

- [9] B. M. Wilamowski, "A Novel Concept of Neuristor Logic," <u>International Journal</u> of <u>Electronics</u>, Vol. 33, No. 6, June 1972, pp. 659 - 653. [10] J. Gutierrez, J. Mulet, and W.

- [10] J. Gutierrez, J. Mulet, and W. Warzanskyj, "Boolean Multiple-Valued Logic Based on Neuristor Properties," Froceedings of the 26th Midwest Symposium on Circuits and Systems, August 1983, pp. 66 69.

- [11] S.-Y. Kung, "On Supercomputing with Systolic/Wavefront Array Processors," Proceedings of the IEEE, Vol. 72, No. 7, July 1984, pp. 867 884.

FIGURE 1 SOLITON PULSES

FIGURE 2

FIGURE 3

FLOW GRAPH OF MIN CELL

1-1

# 1985 IEEE WORKSHOP ON LANGUAGES FOR AUTOMATION

COGNITIVE ASPECTS IN INFORMATION PROCESSING

UNIVERSITAT DE PALMA PALMA DE MALLORCA, SPAIN JUNE 28-29, 1985

D IEFE COMPUTER SOCIETY