### ABSTRACT

| Title of Thesis:    | AN EVALUATION OF EMBEDDED SYSTEM BEHAVIOR                                     |  |

|---------------------|-------------------------------------------------------------------------------|--|

|                     | USING FULL-SYSTEM SOFTWARE EMULATION                                          |  |

| Degree Candidate:   | Christopher Michael Collins                                                   |  |

| Degree and Year:    | Master of Science, 2000                                                       |  |

| Thesis Directed by: | Professor Bruce L. Jacob<br>Department of Electrical and Computer Engineering |  |

With embedded processor technology moving towards faster and smaller processors and systems on a chip, it becomes increasingly difficult to accurately evaluate realtime performance. This research describes an evaluation method using an embedded architecture software emulator that models the Motorola M-CORE processor architecture. This emulator is used to evaluate and compare the real-time performance of a public-domain experimental Real-Time Operating System (RTOS) against a bare-bones multi-rate task scheduler. The results of the experiment, as shown in arrival time JIT-TER, response-time DELAY, and CPU BREAKDOWN figures, show the trade-offs between job load, job frequency, and kernel overhead. This research suggests full-system software emulation to be a valid method of evaluating embedded systems' behavior and real-time performance.

### AN EVALUATION OF EMBEDDED SYSTEM BEHAVIOR

## USING FULL-SYSTEM SOFTWARE EMULATION

by

Christopher Michael Collins

Thesis submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Master of Science 2000

Advisory Committee:

Professor Bruce L. Jacob, Chair Professor Shuvra S. Bhattacharyya Professor Donald Yeung

#### ACKNOWLEDGEMENTS

I would like to thank Eric Fiterman and Tiebing Zhang for their assistance in the research that led up to this report. They both aided in the creation of the emulator and spent many hours debugging and running simulations.

I would like to thank Moussa Ba, Julian Requejo, Sujaya Srinivasan, and Dr. David B. Stewart in the SERTS lab for their assistance with their Echidna operating system and the Motorola M-CORE evaluation board.

I would like to thank Dr. Bruce L. Jacob for giving me the opportunity to work on this project and for many hours of assistance with the research itself in addition to the development of this report.

On a personal note, I would like to thank my parents, John and Joan M. Collins, for their support and understanding throughout this project.

Finally, I would like to thank Danesha R. Fitzgerald, for her support, for keeping me sane, and most importantly, for believing in me.

# TABLE OF CONTENTS

| List of Tables                                          | vi   |

|---------------------------------------------------------|------|

| List of Figures                                         | vii  |

| List of Abbreviations                                   | viii |

| Chapter 1: Introduction                                 | 1    |

| 1.1: Goal and Motivation                                | 1    |

| 1.2: Results                                            | 4    |

| 1.3: Overview of Report                                 | 5    |

| Chapter 2: Background                                   | 6    |

| 2.1: Embedded Systems                                   | 6    |

| 2.1.1: Embedded Systems versus General Purpose Systems  | 7    |

| 2.1.2: Design Issues                                    | 7    |

| 2.1.3: Development Tools                                | 9    |

| 2.1.4: Embedded System Trends                           | 10   |

| 2.1.4.1: Application Specific Integrated Circuits       | 10   |

| 2.1.4.2: Systems On A Chip                              | 10   |

| 2.1.5: The Emulator's Benefit to Embedded System Design | 11   |

| 2.2: Hardware/Software Codesign                         | 12   |

| 2.2.1: Hardware/Software Codesign: The Concept          | 12   |

| 2.2.2: Hardware/Software Codesign: The Methodology      | 13   |

| 2.2.3: Model Based Codesign                             | 13   |

| 2.2.4: The Emulator's Benefit to                        |      |

| Hardware/Software Codesign                              | 14   |

| 2.3: Real-Time Operating Systems                        | 14   |

| 2.3.1: Real-Time Operating Systems: The Requirments     | 15   |

| 2.3.2: User Tasks and Threads                           | 18   |

| 2.3.3: The Kernel                                       | 19   |

| 2.3.4: Synchronization and Communication                | 20   |

| 2.3.5: The Emulator's Benefit to                        |      |

| Real-Time Operating Systems                             | 20   |

| 2.4: Evaluation of Real-Time Systems                    | 20   |

| 2.4.1: Methods of Evaluation                            | 21   |

| 2.4.2: Metrics of Characterization                      | 21   |

| 2.4.3: Current Studies                                  | 22   |

| 2.4.4: The Emulator's Benefit to the Evalation          |      |

| of Real-Time Systems                                    | 22   |

| 2.5: SimOS                                              | 22   |

| 2.5.1: The SimOS Approach                               | 23   |

| 2.5.2: Studies Performed with SimOS                     | 24   |

| 25 |

|----|

| 26 |

| 26 |

| 32 |

| 32 |

| 33 |

| 35 |

| 35 |

| 36 |

| 37 |

| 37 |

| 37 |

| 38 |

| 39 |

| 40 |

| 41 |

| 45 |

| 45 |

| 46 |

| 48 |

| 49 |

| 49 |

| 49 |

| 49 |

| 50 |

| 50 |

| 50 |

| 51 |

| 53 |

| 53 |

| 54 |

| 62 |

| 68 |

| 72 |

| 79 |

| 79 |

| 80 |

| 83 |

| 86 |

| 86 |

| 87 |

| 89 |

| 91 |

|    |

| 5.4: A      | nalysis Summary        | 91  |

|-------------|------------------------|-----|

| Chapter 6:  | Conclusions            | 93  |

| Chapter 7:  | Future Work            | 96  |

| Appendix A: | M-CORE Instruction Set | 98  |

| References  |                        | 102 |

# LIST OF TABLES

| 1.   | Test Applications   | 43 |

|------|---------------------|----|

| A-1. | M-CORE instructions | 98 |

## LIST OF FIGURES

| 1.  | The SimOS Environment.                                  | 24 |

|-----|---------------------------------------------------------|----|

| 2.  | The Emulation Environment.                              | 27 |

| 3.  | Instruction Format.                                     | 28 |

| 4.  | User Program Model and Supervisor Additional Resources. | 31 |

| 5.  | Format of an ELF file.                                  | 33 |

| 6.  | The M-CORE pipeline.                                    | 35 |

| 7.  | Output Example.                                         | 42 |

| 8.  | NOS Main Loop.                                          | 48 |

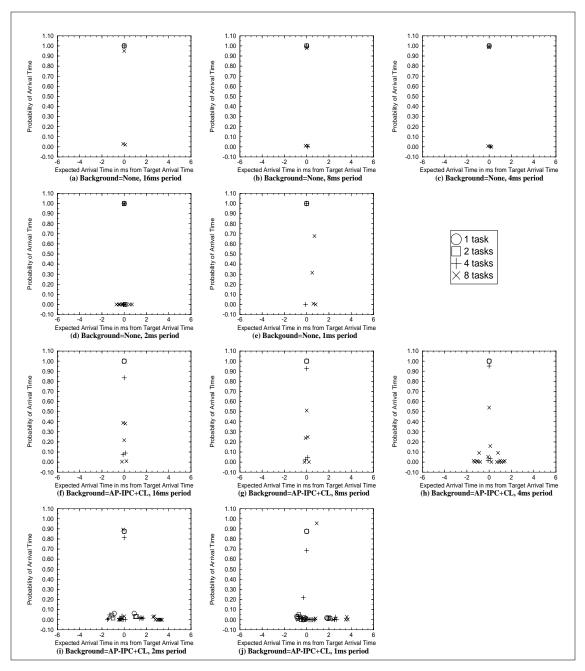

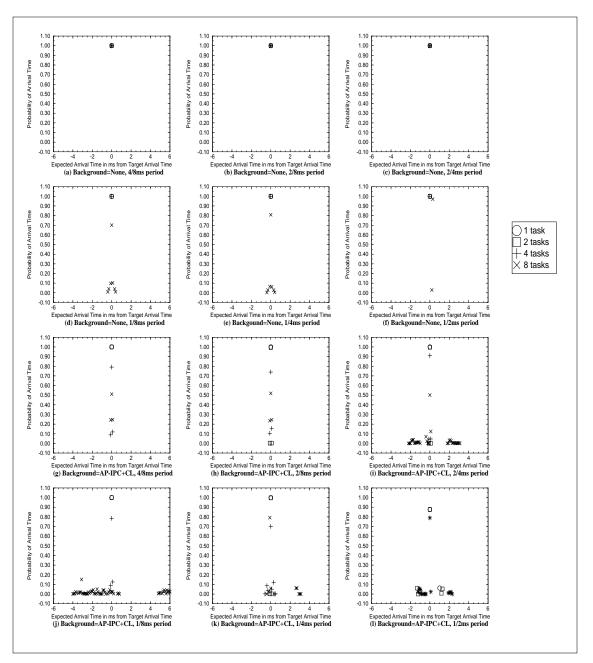

| 9.  | JITTER probability density graphs for P-IPC on Echidna. | 55 |

| 10. | JITTER probability density graphs for P-IPC on NOS.     | 60 |

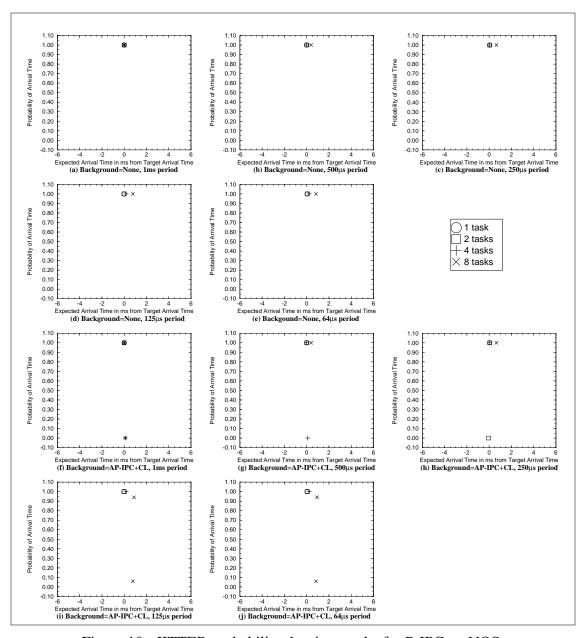

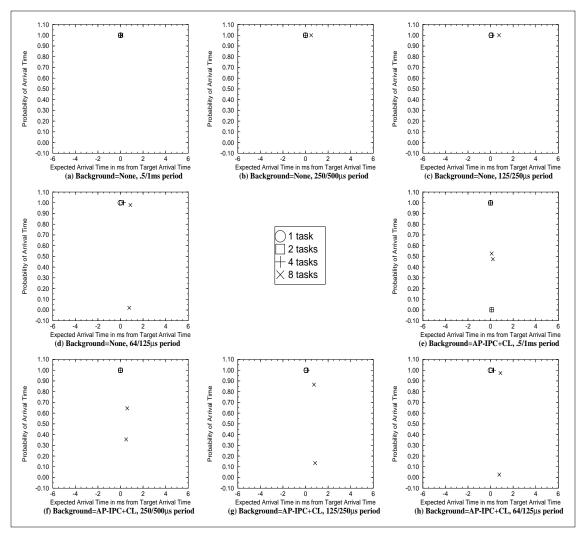

| 11. | JITTER probability density graphs for UP on Echidna.    | 63 |

| 12. | JITTER probability density graphs for UP on NOS.        | 66 |

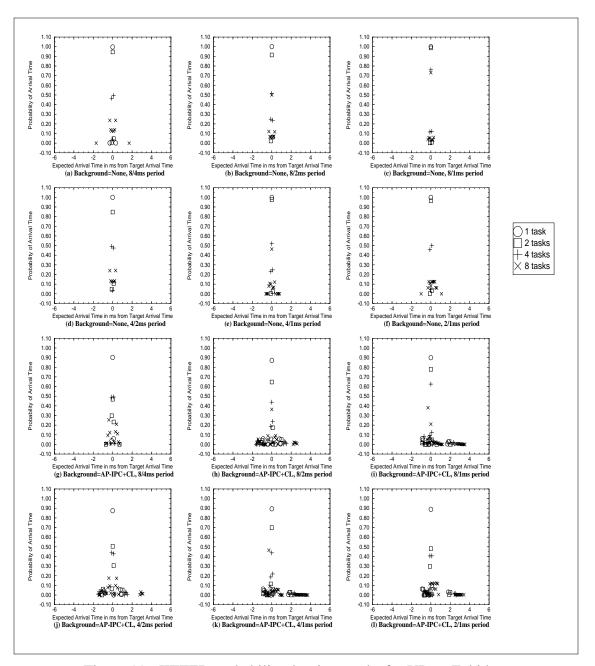

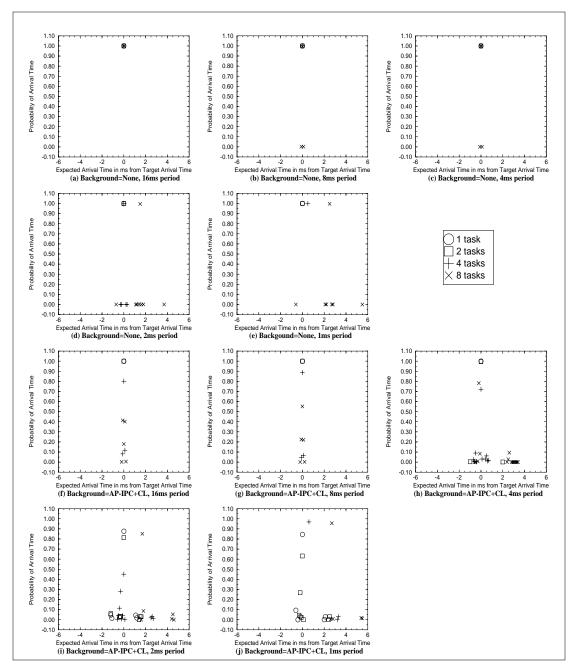

| 13. | JITTER probability density graphs for DOWN on Echidna.  | 69 |

| 14. | JITTER probability density graphs for DOWN on NOS.      | 71 |

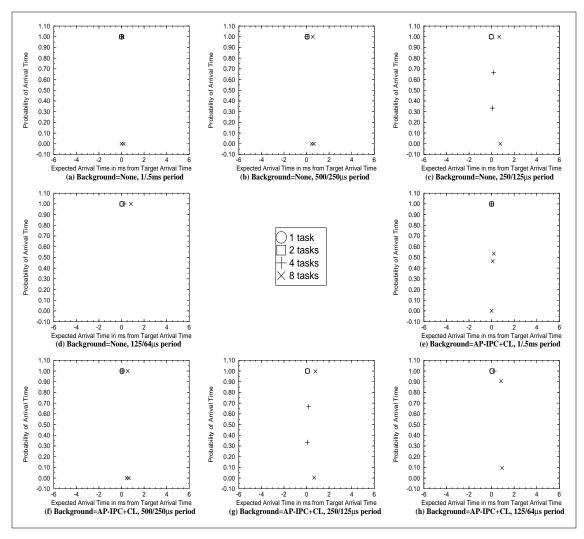

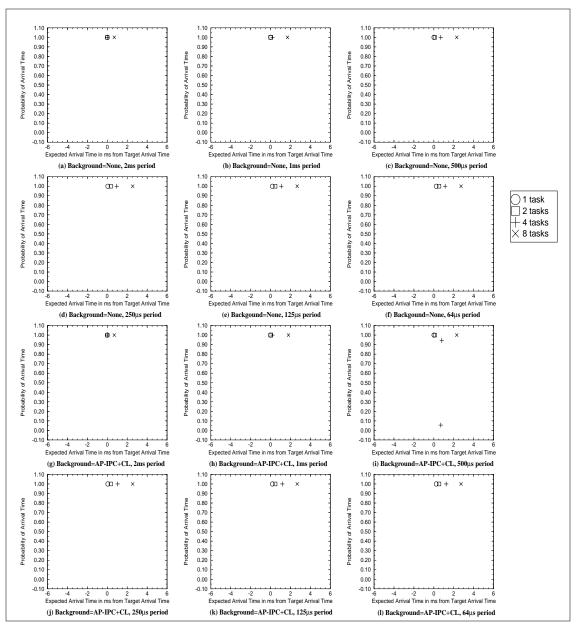

| 15. | JITTER probability density graphs for FIR on Echidna.   | 74 |

| 16. | JITTER probability density graphs for FIR on NOS.       | 77 |

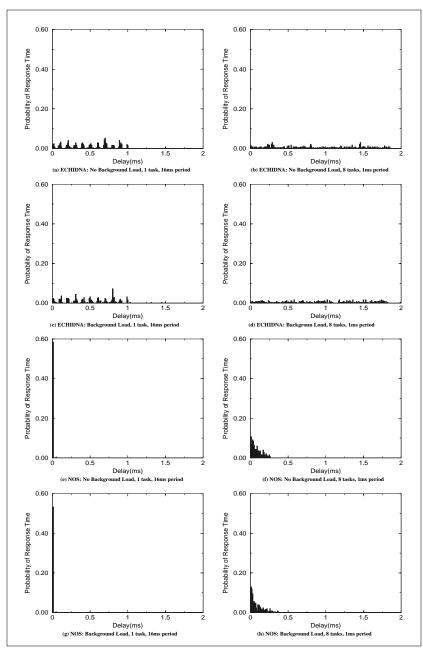

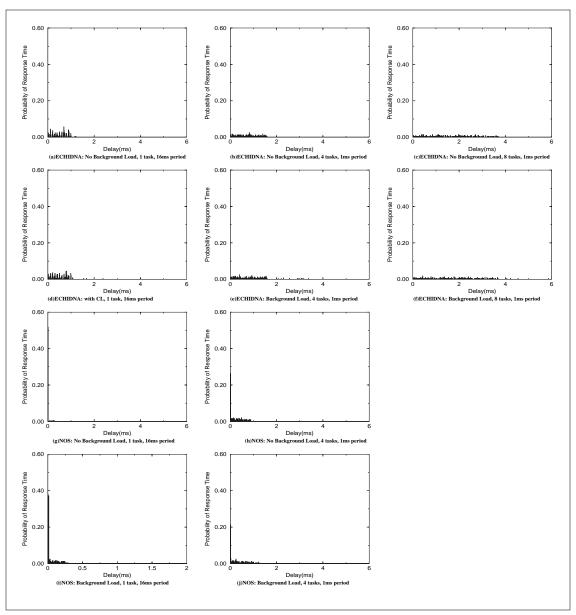

| 17. | Delay probability density graphs for P-IPC.             | 81 |

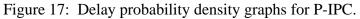

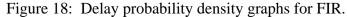

| 18. | Delay probability density graphs for FIR.               | 84 |

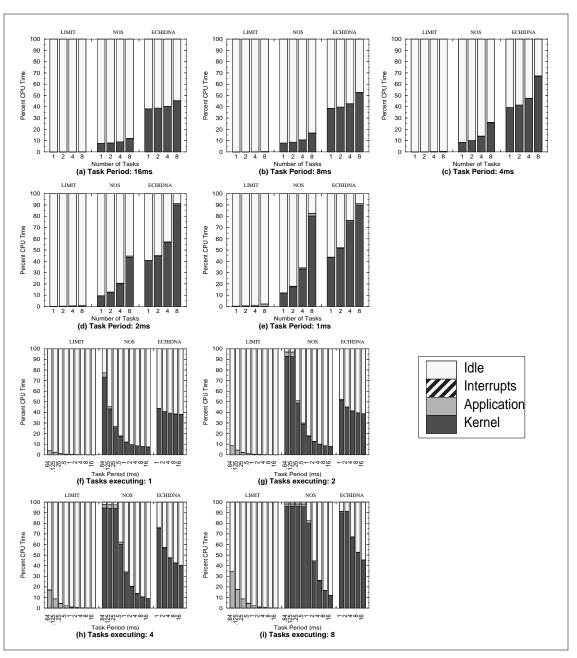

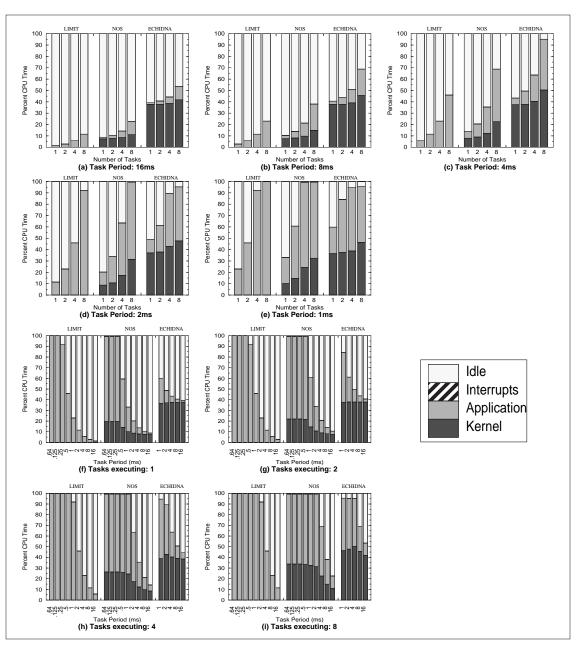

| 19. | CPU-BREAKDOWN graphs for P-IPC.                         | 88 |

| 20. | CPU-BREAKDOWN graphs for FIR.                           | 90 |

# LIST OF ABBREVIATIONS

| ASIC   | Application Specific Integrated Circuit                                                     |

|--------|---------------------------------------------------------------------------------------------|

| AP-IPC | Aperiodic Inter-Process Communication                                                       |

| CL     | Control Loop                                                                                |

| CPU    | Central Processing Unit                                                                     |

| ELF    | Executable-Linking Format                                                                   |

| EPC    | Exception Program Counter                                                                   |

| EPSR   | Exception Program Status Register                                                           |

| EX     | Execution Stage                                                                             |

| EXWB   | The boundary between the Execution and<br>Write Back stages                                 |

| FPC    | Fast Interrupt Program Counter                                                              |

| FPSR   | Fast Interrupt Program Status Register                                                      |

| ID     | Instruction Decode Stage                                                                    |

| IDEX   | The boundary between the Instruction Decode and Execution Stages                            |

| IC     | Integrated Circuit                                                                          |

| IF     | Instruction Fetch Stage                                                                     |

| IFID   | The boundary between the Instruction Fetch and<br>Instruction Decode stages                 |

| IPC    | Inter-Process Communication                                                                 |

| IRAM   | Intelligent RAM                                                                             |

| FIR    | Finite Impulse Response                                                                     |

| MAIN   | The boundary before the Instruction Fetch stage,<br>the instruction about to enter the pipe |

| NOS   | Non-Operating System                                                  |

|-------|-----------------------------------------------------------------------|

| PC    | Program Counter                                                       |

| PSR   | Program Status Register                                               |

| RAM   | Random Access Memory                                                  |

| ROM   | Read-Only Memory                                                      |

| RTOS  | Real-Time Operating System                                            |

| SOC   | System on a Chip                                                      |

| VBR   | Vector Base Register                                                  |

| WB    | Write Back Stage                                                      |

| WBEnd | The boundary after the WB Stage, when the instruction leaves the pipe |

## Chapter 1: Introduction

With embedded processor technology moving towards faster and smaller processors and systems on a chip, it becomes increasingly difficult to accurately evaluate realtime performance. Probing a piece of silicon, or accurately measuring values approaching less than one nanosecond becomes more expensive and more difficult, if not impossible. It becomes necessary to find additional methods to evaluate and debug embedded systems.

### 1.1: Goal and Motivation

The goal of this research is to provide an additional method for evaluating and debugging embedded systems. This research presents a method of using full-system emulation to evaluate the real-time performance of an embedded system. An embedded architecture emulator was created, using the C programming language, that emulates the Motorola M-CORE embedded processor down to the register level and is accurate to within 100 cycles per million as compared to actual hardware. This work touches on several different aspects of embedded systems design, such as the testing and debugging of increasingly integrated systems, hardware/software codesign methodologies, and the evaluation of real-time systems.

One of the motivators of this research is that it is becoming increasingly difficult to evaluate system behavior at the hardware level. Apart from the unpleasantries of

waiting for actual fabrication of the hardware, or the expense of such a task, it is sometimes difficult to obtain information from the actual hardware. Five, ten years ago it was easy enough to hook up a probe to the bus connecting the processor to the main memory or the connections between the processors and other pieces of the hardware. However, with the advent of systems on a chip and application-specific integrated circuits, it is no longer possible to obtain those signals, for they never leave the silicon [32, 45]. The only way to debug these systems is to either probe the silicon itself, or to add additional logic to the chip so that it brings the signal off the chip, and even that option is limited by the number of physical pins that can be put on a chip and spared for simple debug and evaluation purposes. Also, with the speeds that some of today's embedded processors are running, it becomes difficult to find a logic analyzer that can keep up with the processors, not to mention costing tens to hundreds of thousands of dollars [20, 29]. If there were another method to evaluate these systems early on, both valuable time and money could be saved.

One of the methodologies gaining wide acceptance in both the embedded world and the general purpose world is that of hardware/software codesign [24]. As opposed to the traditional methods of developing the hardware and software for a system separately, the hardware/software codesign methodology recognizes the benefits inherent in the designing of the two together, at the same time. The hardware being designed with the software needs in mind as well as the designing of the software with hardware limitations and issues in mind benefit the design both in performance and time to market, given that if hardware and software designers communicate during the design process, there is less chance of problems happening due to ignorance [9]. This research offers a

method for the software engineer to test his software on a C emulator, something that he will understand, as opposed to handing the software off to a technician to go run it on the actual hardware, or for him to try to understand how to operate a VHDL model.

Real-Time Operating Systems are commonly used in the development, productizing, and deployment of embedded systems. Unlike the world of general purpose computing, embedded systems are usually developed for a limited number of tasks. Any facilities that these tasks might need are often built directly into the code and the feeling is often that real-time operating system would just add unnecessary overhead [13]; in many cases, any RTOS functionality needed is provided by a homegrown design. However, these "roll-your own" [13] pseudo operating systems that are created on the fly are not very portable and often times include additional work that could easily be accomplished by using one of today's many commercial RTOSs. What is needed is a method to test both commercially available Real-Time Operating Systems and in-house creations on the target architecture to verify which would give the best behavior.

Many of the projects in the area of real-time systems concern themselves with the development of scheduling algorithms and the demonstration that those algorithms work [1,2,53,54]. However, as others have observed [28], "there currently exists a wide gap between real-time scheduling theory and the reality of RTOS implementation." The majority of the work in this field is done through theoretical analysis testing the scheduler code at the block level, or running the raw scheduler code by itself. Very little of that analysis follows those scheduling algorithms all the way to the RTOS implementation, where other mechanisms like inter-process communication and semaphores interact in subtle ways to make the behavior of the algorithms less easily understood and

therefore less predictable. The analysis of these scheduling algorithms should be accompanied with experimental evaluation of RTOSs on the actual hardware. Unfortunately, this sometimes presents a problem when the hardware is not available, or there are questions of money or time. However, if it was possible to run tests on an emulation of that hardware, that would save both time and money and allow this analysis to be complete.

The research effort going on currently that most resembles this work is the SimOS project going on at Stanford [44]. Like the emulator described in this research, SimOS is an execution driven simulator that is accurate enough to run a full operating system on top of it. The primary difference between the emulator developed for this research and SimOS is the target application domain. SimOS is focused on studying high performance machines, while the emulator created for this work is interested in evaluating the real-time performance of low power embedded processors.

1.2: Results

In this research, an embedded system emulator was built in C. A study of two Real-Time Operating Systems was run on that emulator. Echidna [10] is a publicly available RTOS based on Chimera [48]. NOS is a fixed-priority, multi-rate executive [27] based on descriptions of bare-bones RTOS given by designers in the industry [13].

This study provides information about both of the RTOSs that might lead to a decision among them as to which one to use. Predictably, as loads increased, the RTOSs hit their job deadlines until system loads were reached and missed those deadlines afterwards. Also predictably, as the system became overloaded in NOS, lower priority tasks were completely ignored. It is seen that RTOS overheads are extremely high when com-

pared to low overhead tasks. In some cases, the RTOS can account for more than 90% of the processor's busy time. However, as the periodic task's complexities and CPU requirements grow, the proportion of the RTOS diminished significantly, to a point where the RTOS accounts for only 20-50% of the processor's busy time. Lastly, this study has shown that this method of using a full-system software emulator can be used as a valid method for the evaluation of embedded system behavior.

### 1.3: Overview of Report

Chapter 2, Background, describes the work that has been done in this field and areas that relate to this field of research. Chapter 3, The Emulator, gives a detailed description of the emulator, the steps that went into making it, and the methods used to verify it. Chapter 4, Real-Time Performance Evaluation, first describes the two different Real-Time Operating Systems that were run on the M-CORE Emulator, Echidna and NOS, describes the four benchmarks that were run on each of the real-time operating systems, describes the two types of background load run on the real-time operating systems, and describes the experiment. Chapter 5, Results and Analysis, displays the results from the experiment listed in Chapter 4, and analyzes the different results for the several benchmarks. Chapter 6, Conclusions, gives the conclusions drawn from the findings of this paper, and Chapter 7, Future Work, describes possible continuation of this work.

## Chapter 2: Background

This chapter offers a brief background into the areas that are related to the research performed in the report as well as the areas that support the reasons for performing this research. The first section takes a look at embedded systems, the issues and tools involved in their design, current trends, and how they can benefit from this research. The second section examines Hardware/Software Codesign, the methodologies that it has produced, and how those methodologies can benefit from this research. The third section gives an introduction to real-time operating systems and breaks down the issues involved in their creation and use. Section four discusses the evaluation of real-time systems, the methods used to evaluate those systems, the metrics used to characterize them, and the current studies going on in the field. In the final section of this chapter, SimOS, a full-system simulation very much like the emulator created in this research is described, and the studies that have been performed with it are listed, as well as how it differs from the emulator created in this research.

### 2.1: Embedded Systems

Embedded systems has become a buzz word in the last five years, but embedded systems and processors have been around for much longer than that [46]. One only needs to look around to see embedded systems everywhere: cell phones, alarm clocks, personal data assistants(PDAs), automobile subsystems such as ABS and cruise control,

etc. This section takes a look at embedded systems, the issues and tools involved in their design, current trends, and how they can benefit from the research performed for this report.

### 2.1.1: Embedded Systems versus General Purpose Systems

An embedded system is usually classified as a system that has a set of predefined, specific functions to be performed and in which the resources are constrained [46]. Take for example, a digital wrist watch. It is an embedded system, and it has several readily apparent functions: keeping the time, perhaps several stopwatch functions, and an alarm. It also has several resource constraints. The processor that is operating the watch cannot be very large, or else no one would wear it. The power consumption must be minimal; only a small battery can be contained in that watch, and that battery should last almost as long as the watch itself. And finally, it must accurately display the time, consistently, for no one wants a watch that is inaccurate. Each embedded design satisfies its own set of functions and constraints. According to [46], there are an estimated 50,000 new embedded designs a year.

This is different from general purpose systems, such as the computer that sits on a desk in an office. The processor running that computer is termed a "general purpose" processor because it was designed to perform many different tasks well, as opposed to an embedded system, that has been built to perform a few specific tasks either very well or within very strict parameters.

### 2.1.2: Design Issues

As mentioned above, embedded systems are defined by their functions and their constraints. These constraints are almost as varied as the number of embedded systems

themselves, but a few of the more prevalent ones are response time accuracy, size, power consumption, and cost [46]. All of these present the embedded system designer with some difficult decisions.

Response time is a critical factor in many embedded systems. Whether it is a specific time that an embedded system tasks needs to be run, like that of the alarm on an alarm clock; or the time between tasks that is important, like the system that delivers pain medication to a burn victim; all of these are time-critical issues. The most difficult task for an embedded system designer to do is to quantify these time deadlines, decide whether these deadlines are firm, and recognize what the consequences are if these deadlines are not met.

Size, as mentioned above, is also an important decision in many embedded systems. Many embedded systems designed today are bought and sold simply because they are smaller than the last implementation of that product. Take for example, the cellular phone. Today's cellular phones are half the size of the phones available two years ago, and those phones two years ago were smaller than the phones available before them. So if the manufacturer does not take into account size when designing his cell phone, he will most likely go out of business shortly after he produces a cell phone that is two to three times the size of all of his competitor's phones.

Another design issue concerning today's embedded system designers is that of power consumption. Continuing along the same line as the above mentioned size factor, many of these devices that are very small are handheld devices that are made to be mobile and thus must have a battery. Since the designer does not want the user to be forced to plug in or recharge the device every five minutes, the designer must make

important choices in his design decisions and balance a feature's merits against the power that the feature will consume.

A final consideration that embedded designers deal with is cost. Regardless of any choice of the above issues made, an embedded product is not going to sell if its cost is exorbitant. Most end users will sacrifice a small amount of performance, or a slightly less amount of battery time, for an embedded product that is less costly than all of its competitors. So just as with all of the above considerations, the designer must consider the cost of adding a particular modification to the design and whether or not the end user will be willing to pay that additional cost for that additional feature.

2.1.3: Development Tools

Embedded development tools have traditionally lagged behind tools for the development of general systems [46]. Unlike general systems, the design space for embedded systems is extremely large, so it is difficult to contain all of the facilities to specify, design, and test embedded systems.

However, now that embedded systems have garnered more interest in the research community as well as there being an increased need for those embedded systems, embedded systems tools are now catching up with regular system design tools, and they have become more readily available and diverse in their area of coverage [46]. Tools that were not available 5 to 10 years ago are now available as part of common EDA development suites. Also, tools are now available for the development of embedded system application software as well as the development of real-time operating systems.

### 2.1.4: Embedded System Trends

With the increase in interest and research of embedded systems have come a flood of new design trends. It is hard to envision that five years from now embedded systems will bear much resemblance to the systems today [46], other than their basic functionalities, and even those may be replaced in the future. Two of the trends currently hot in the embedded systems world that are discussed here are that of application specific integrated circuits (ASICs) and systems on a chip (SOC).

#### 2.1.4.1: Application Specific Integrated Circuits

The best way to define an application specific integrated circuit (ASIC) is to saying what it is not: an integrated circuit designed for multiple uses. Like the title suggests, this is a IC that has been designed for a specific application. Examples of ICs that are not ASICs are standard computer parts such as RAM, ROM, multiprocessors, etc. Examples of ICs that are ASICs are a chip designed for a toy robot or a chip designed to examine sun spots from a satellite [45].

The reason for mentioning this is that since ASICs are developed for a specific purpose, they are most likely constrained with both a tight budget and a short time to market. Any and all methods that might aid in the development of these chips would be welcomed with open arms in the industry.

#### 2.1.4.2:System On A Chip

System on a chip (SOC) is exactly what it sounds like. Hardware designers have taken the normally separate pieces of a complete system; the CPU, memory controller, main memory, I/O control, and the various buses and interconnects, and placed many or

all of them on a single piece of silicon. This has the added benefits of size reduction, power reduction, cost reduction, and time delay reduction.

On of the more popular forms of SOC is that of Dave Patterson's Intelligent-RAM (IRAM) [20, 29]. IRAM is the combination of a processor on a chip with a large area of DRAM instead of or in addition to cache. This concept has several advantages. Like all forms of SOC, it reduces the number of chips in a system, allowing the product to be smaller and less expensive. IRAM addresses the key bottlenecks in many systems: memory bandwidth and memory latency. Memory bandwidth on IRAM is four times as wide as that on traditional systems, and memory latency is considerably less than that of traditional systems since the signals do not need to cross a pin barrier that can have a maximum number of pins.

However, there are also several inherent difficulties with SOC and IRAM. One is that there is only so much area on a chip, and this limits what you can put on it. It puts upper limits on the amount of main memory that you can have with a system, unless you still want to rely on going off-chip occasionally for information. Another large problem is that the design team creating the system on a chip must contain all of the knowledge to create a processor, a main memory, a I/O controller, and optimize all of them together [3, 32].

### 2.1.5: The Emulator's Benefit to Embedded System Design

One of the problems with embedded systems, and more specifically ASICs and SOCs, is that it is no longer possible to obtain debug information that was readily available in systems with discrete components. Those signals that are contained only in the silicon, such as information across the memory bus, never leave the silicon. The only

way to debug them is to either probe the silicon itself, or to add additional logic to the chip that brings the signal off the chip, and even that option is limited by the number of physical pins that can be put on a chip and spared for simple debug and evaluation purposes. Also, with the speeds that some of today's embedded processors are running, it becomes difficult to find a logic analyzer that can keep up with the processors, not to mention costing tens to hundreds of thousands of dollars [20, 29]. If there were another method to test these system, both valuable time and money could be saved. The emulator that has been designed for this report could be used as an additional method to test those systems without incurring additional time and cost.

### 2.2: Hardware/Software Codesign

One of the methodologies gaining wide acceptance in both the embedded world and the general purpose world is that of Hardware/Software codesign [24]. This section first defines the concept and then the methodology of Hardware/Software codesign. Then a slightly different method of codesign is described. This section is concluded with how Hardware/Software Codesign can benefit from the emulator developed in this research.

### 2.2.1: Hardware/Software Codesign: The Concept

For years, designers have partitioned systems into hardware and software components that were developed separately [16]. When this is done, the hardware designers usually make architectural choices early in the design process. These decisions are based on their knowledge of the hardware requirements and their limited knowledge and understanding of the software requirements. And they are usually hard pressed to go back and make changes to these choices [18]. The result is that often the software

designers are forced to make up for problems in the hardware through additional work of the software, often leading to a less than optimal overall design of the system.

The concept of Hardware/Software Codesign is that of both hardware and software designers work together to develop a system, whether that system be an embedded one, a general purpose one, or high performance one [9,24]. From specification of the requirements to exploration of the design space, and from development of the physical design to the simulation and test of the final product, hardware and software designers work cooperatively, concurrently, and most importantly, they communicate [9].

### 2.2.2: Hardware/Software Codesign: The Methodology

In response to these problems listed above, designers as well as EDA tool manufacturers are moving towards a design methodology that has hardware and software engineers working together from the beginning of the specification phase all the way through simulation and test [12]. In hardware/software codesign, designers from both disciplines integrate their work. The process begins with a functional exploration of the project that they are undertaking. The designers define requirements and create a working specification. Then the hardware and software designers work together to map this specification on hardware and software architectures. The designers then implement these architectures onto silicon and code and come back together to simulate and test. The entire process benefits from open communication from both sides [11,12].

### 2.2.3: Model Based Codesign

Another popular method of hardware/software codesign that is gaining greater acceptance is that of model based codesign. Model based codesign includes all of the above steps, but all of the work is done using mathematical models on a computer. This

gives the added benefit of being able to run the above process multiple times, i.e. iterate on the design. Each time the process runs with slight modifications, and through many of these simulations, the optimal system is found. The benefit of this methodology is that the designer does not have to wait while a physical design is being created or suffer the cost of implementing that design. Often times this model based codesign is automated, leaving the designers even more time to perform other tasks. However, the down-side of model based codesign is that it is a mathematical representation of the real world: many mathematical representations are only approximate [43].

### 2.2.4: The Emulator's Benefit to Hardware/Software Codesign

As mentioned above, one of the most difficult tasks for engineers to do is to bridge the gap of knowledge between hardware and software designers. The research that we are performing offers an aid for the software engineer in that he can test his software on a C emulator, something that he will understand, as opposed to handing the software off to a technician to go run it on the actual hardware, or for them to try to understand how to operate a VHDL model. This research offers the hardware engineer a tool that allows him to quickly evaluate architectural changes without having to re-fab the microprocessor or other pieces of the system's hardware.

### 2.3: Real-Time Operating Systems

Real-Time Operating Systems (RTOS) are commonly used in the development, productizing, and deployment of embedded systems. Unlike the world of general purpose computing, real-time systems are usually developed for a limited number of tasks and have different requirements of their operating systems [5,14,15]. This section first gives the requirements of real-time operating systems, then breaks down the internals of

RTOSs and explains them in detail. This section concludes with how the emulator developed in this research would aid in the evaluation of RTOSs.

### 2.3.1: Real-Time Operating Systems: The Requirements

According to Liu [34], a good RTOS not only offers efficient mechanisms and services to carry out real-time scheduling and resource management but also keeps its own time and resource consumption predictable and accountable. A RTOS is responsible for offering the following facilities to the user programs that will run on top of it. The first responsibility is that of scheduling: a RTOS needs to offer the user a method to schedule his tasks. The second responsibility is that of timing maintenance: the RTOS needs to be responsible in both providing and maintaining an accurate timing method. The third responsibility is to offer user tasks the ability to perform system calls: the RTOS offers facilities to perform certain tasks that the user would normally have to program himself, but the RTOS has them included in its library, and these system calls have been optimized for the hardware system that the RTOS is running on. The last thing that the RTOS needs to provide is a method of dealing with interrupts: the RTOS needs to offer a mechanism for handling interrupts efficiently, in a timely manner, and with an upper bound on the time it takes to service those interrupts [34, 46].

There are several concepts that need to be defined in any discussion of RTOSs. The first concept is that of preemption. Real-time operating systems are either preemptive or non-preemptive. If a real-time operating system is preemptive, it means that a task currently being run by the RTOS can be interrupted by another task with a higher priority or an external interrupt. The interrupted task's state is saved, and this state will be restored when it is run again, allowing it to continue along from the same point that it

was interrupted. RTOSs that are nonpreemptive cannot be interrupted. If a task is currently running when a second task needs to run, that second task must wait for the first task to finish running before it can begin to run [46].

Another important concept is that of hard real-time versus soft real-time. Hard real-time means that a task must always be completed by a specific time. The integrity of the system designed with hard real-time tasks will be compromised if such a deadline is missed. An example of this is the communication mechanism from the cockpit of a commercial airliner to the embedded system controlling the wing flaps. If a pilot is coming in for landing, and pulls up on his flaps to slow his descent, that communication must work — for if it doesn't, the entire plane has the possibility of crashing. Soft real-time systems are any type of system that is not a hard real-time system, meaning that if a task is late, the system will continue to keep running. An example of this is an Automated Teller Machine (ATM). If the software running upon the ATM takes a little longer to process a request, other than the costumer being slightly upset, the system will be able to perform its tasks, albeit late [46].

There are several different types of task scheduling for today's real-time operating systems to choose from. There is the endless loop scheduler, that is basically a while(1) loop that continuously runs a piece of code. Activities within the loop are executed in sequence and as many times as possible. The next level of task scheduling is that of the basic cyclic executive scheduler. In a basic cyclic scheduling algorithm, the idea of the endless loop is extended in that designers can separate the code to be executed into separate tasks. These tasks execute in a standard sequence in an infinitely repeating loop. This type of scheduling is often called round-robin scheduling. Like the

endless loop, all of the tasks run as often as possible. Time driven cyclic scheduling, the next level of task scheduling, differs from basic cyclic in that instead of running each one of these tasks as often as possible, it introduces the idea of a time interrupt. In this scheduler, one hardware timer is used to wake up all tasks. This timer wakes up the first task in line, and as soon as that first task is finished, the next task runs. All of the tasks in line must finish before the next timer interrupt. Following the time driven cyclic scheduler is the multi-rate cyclic executive scheduler. This is an expansion of the time driven cyclic scheduler in that it allows multiple periods, so long as higher frequency tasks are a multiple of the base task's frequency. This is done by inserting a task more than one time into the chain or into multiple chains. The multi-rate executive for periodic tasks scheduler adds the ability to have multiple periods by instituting a timer that is the lowest common multiple of all of the periods of all of the tasks. At each tick of this timer, tasks can be made to execute. All of the above scheduling algorithms usually deal with interrupts by inserting tasks that poll for them, and all of the above scheduling algorithms are nonpreemptive. A multi-rate executive with interrupts allows external interrupts to break into current execution and be serviced. The task interrupted is then restarted when the interrupt is done. Finally, the priority based preemptive executive scheduler is the same as the multi-rate executive with interrupts except that it allows not only interrupts to break into the current program, but tasks with higher priority as well [27].

Scheduling algorithms are either static or dynamic. Static scheduling is performed when the execution times of all tasks to be scheduled by the scheduler are determined before any execution has taken place. Static scheduling is done when the

deadlines for all of the tasks are known, and the time that it takes to execute those tasks is also known. All of the scheduling is done offline, before the execution of any tasks has begun, and is fixed. Dynamic scheduling is performed when the execution time of the tasks to be run is not fixed, is variable, and scheduling orders and priorities must be done dynamically during execution. This is done when task priority, execution time, or deadlines either change during execution, or are unknown before execution begins. The order in which tasks are scheduled and executed is decided upon during runtime, and is variable [34].

### 2.3.2: User Tasks and Threads

In RTOSs, user tasks are implemented in the form of threads. Each thread implements a computation job and is the basic unit of work handled by the scheduler. When the kernel creates a thread, it allocates memory to that thread and brings in the user code to be executed by that thread. The two different types of threads are periodic and aperiodic. Obviously, aperiodic threads run only once while periodic thread runs continuously at a given frequency [34].

Their are five major states of threads. The first is sleeping: this is when a task is set to sleep for a certain amount of time before it is to be woken up and run. The second state is ready: this is when the thread is ready to run and is simply waiting for the resources to do so. The third state is that of executing: this is when a thread is currently running on the operating system. The fourth state is that of suspended, or also known as blocked: this is when the task cannot proceed for some reason, such as waiting for another event to occur, or for some value to be brought in. The final state is terminated: this is when a thread has run, and is not to be run again [34].

### 2.3.3: The Kernel

The kernel in any RTOS, as mentioned in the introduction to this section, is responsible for four things. They are scheduling, system calls, timing maintenance, and handling interrupts. The RTOS is responsible for maintaining a schedule for all of the tasks running on it, and one of the above scheduling techniques is usually chosen. A system call is any function that the kernel might do at the request of a user thread. To perform a system call, the user task places the name or ID of the function that it wishes to run in a preset location and then traps to the kernel. After the context switch has taken place, the kernel looks up the function that it has been asked to complete, completes it, and puts the result of that function, if there is one, in a second preset location, and then returns control over to the user process. It is also possible for the user process to make a system call and continue working while the kernel is performing this system call. The kernel is also responsible for maintaining the timer. Every time that a timer interrupt is handled, the kernel must update the time as well as wake up tasks that need to be woken up and put on the ready queue. The last thing that a RTOS is responsible for is the handling of interrupts. Upon a interrupt, the hardware starts the RTOSs exception handler software. The RTOS is then responsible for saving the current state on the stack, determining the type of interrupt that has interrupted normal processing, and to know where that interrupt's service routine is. It then turns over control to that interrupt's service routine. After that routine has finished, the kernel is also responsible for transferring control back to the user process [34].

### 2.3.4: Synchronization and Communication

In addition to all of the above requirements, RTOSs are also responsible to provide methods of synchronization and communication between tasks. Mechanisms such as semaphores, mutexes, and condition variables add the ability for tasks to synchronize amongst themselves. To allow communication between the tasks, mechanisms such as message queues, mailboxes, and shared memory can be provided by the RTOS [34].

### 2.3.5: The Emulator's Benefit to Real-Time Operating Systems

One of the biggest decisions in choosing a RTOS for an embedded system is not which RTOS to choose, but whether or not to use a RTOS. Unlike the world of general purpose computing, embedded systems are usually developed for a limited number of tasks. Any facilities that these tasks might need are often built directly into the code, so many designers believe that a real-time operating system would just add unnecessary overhead [13]. What is needed, and what this research provides, is a method to test both commercially available Real-Time Operating Systems and in-house creations on the target architecture to verify which would give the best performance, without having to run the RTOS on the actual hardware, saving both time and money.

### 2.4: Evaluation of Real-Time Systems

From complex mathematical theories to full system hardware simulation, there are many different ways to evaluate real-time systems. The evaluation of these systems, like research in many fields, usually falls into two parties; theoretical and experimental. While many argue for one over the other, these two fields should not be at odds against each other. They are in fact complementary, and any evaluation cannot really be said to be complete without both having been performed. This section provides both the methods and metrics used to evaluate those real-time systems, provides examples of current research that is being done in the evaluation of real-time systems, and concludes with the benefits that the emulator that was developed for this report can give to the evaluation of real-time systems.

### 2.4.1: Methods of Evaluation

There are varying levels of real-time systems evaluation. The most prevalent ones are the use of analytical models, the simulation of scheduling algorithms, and hardware simulation. Analytical models are mathematical theorems and proofs that model the worst time performance of one or more of the aspects of real-time systems, and by changing certain inputs to these theorems, an optimum performance can be proven. Simulation takes the analytical models one step further in creating a simulation using scheduling theory to experiment with behavior of real-time systems. Finally, hardware tests take the theorems that were postulated by the analytical model and have been simulated through the use of scheduling algorithms, and run tests on the actual hardware to discover any behavior that was not determined through either of the other two methods.

### 2.4.2: Metrics of Characterization

Two of the most common metrics used to characterize real-time systems are jitter and response time. Jitter represents the minimum and maximum time separating successive iterations of periodic tasks. If this inter-arrival time is greater than the period of the task, it means that the task is running late, and this will show up as a positive jitter value. If that inter-arrival time is less than the period of the task, that means that the task is running early, and this will show up as a negative jitter value. Response time is the time that

it takes for a real-time system to respond to an external interrupt and represents the reaction time of the system to an unscheduled event while under load.

### 2.4.3: Current Studies

Simulation and hardware execution of real-time software has been used in many different projects: from validating the accuracy of schedulers and analytical models [2, 8, 30, 33, 53], to measuring worst case execution time of functional blocks in dataflow graphs [17, 19, 22, 31], to measuring the effects of pipelined and superscalar processors on timer analysis [23, 35, 51], and to validating the performance of real-time databases [7, 21, 26]. However, while some simulations are accurate down to cycle behavior, most experiments model systems by using dataflow graphs to represent real-time system behavior.

### 2.4.4: The Emulator's Benefit to the Evaluation of Real-Time Systems

The analysis of these scheduling algorithms should be accompanied with experimental evaluation on the actual hardware. Unfortunately, this sometimes presents a problem when the hardware is not available, or there is a question of money or time. However, with the emulator developed for this research it is possible to run tests on an emulation of that hardware, saving both time and money.

2.5: SimOS

The research effort going on currently that most resembles this work is the SimOS project going on at the SimOS group at Stanford [44]. The sections following will discuss what SimOS is, describe the studies that have been performed using it, and detail the differences that exist between it and the emulator created during this research.

### 2.5.1: The SimOS Approach

SimOS is a full-system simulation environment that is capable of modeling computer hardware in enough detail to run a complete operating system, and all of the applications running on that operating system, on top of it [40]. The SimOS project started in 1992, and was built to study the execution behavior of modern workloads [25]. It is capable of studying both uniprocessor and multiprocessor systems and is used to study and evaluate the performance of high-performance and general purpose computers [42, 44].

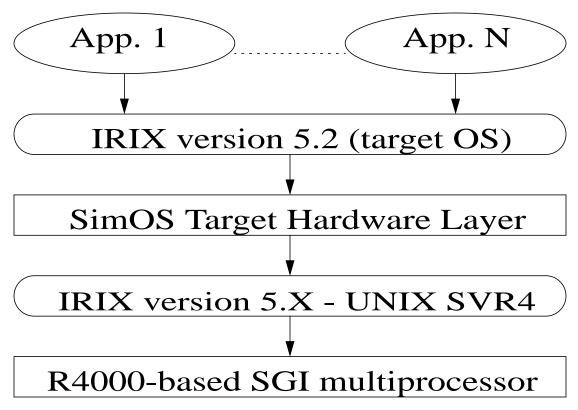

The SimOS environment is a simulation layer that runs on top of general-purpose Unix multiprocessors such as the Silicon Graphics Inc. Challenge series [40]. On top of that general purpose multiprocessor system is the operating system running on that hardware, and in this case, it is IRIX version 5.x. On top of this software is run the SimOS environment. The SimOS environment takes in a hardware description file and is capable of modeling uniprocessors, multiprocessors, RAM, ethernet, hard disk, and other pieces of hardware associated with today's hardware platforms. On top of the SimOS is run an operating system that has been ported to the hardware platform that the SimOS environment is currently modeling. Finally, on top of that operating system is run the unaltered applications programs [40]. All of this can be seen in Figure 1.

One of the advantages of the SimOS operating systems is that it allows the user to choose which level of output detail in which to simulate. The system offers a simple trade-off of speed versus detail of simulation [40]. If the user is interested in obtaining detail simulation results of a particular program, SimOS employs slower, more detailed simulation. And when the user wishes to run an application for long periods of time

Figure 1: The SimOS Environment.

This figure shows the layout of the SimOS development environment. The SimOS target hardware layer runs on top of an Unix Operating System running on a R4000-based SGI multiprocessor workstation. On top of the SimOS environment is run the target Operating System, and any applications that are run on top of that Operating System.

instead of for detailed simulation results, SimOS can scan over unimportant parts of the workload. Also, SimOS allows the user to modify this choice on-the-fly. The user can choose certain sections of code that he is interested in seeing the simulation results for,

and scan over the rest of the code as unimportant[44].

2.5.2: Studies Performed with SimOS

This SimOS simulator has been used in a variety of different research studies.

SimOS has aided studies in the areas of architectural evaluation, such as the study of the

Stanford FLASH multiprocessor. With the detailed model provided by SimOS,

researchers within this project have examined the performance impacts of several of

their design decisions. SimOS has helped studies of system software development, such as in the development for an operating system for the above mentioned FLASH multiprocessor. Having the ability to run on the operating system on the SimOS simulated hardware has provided a more complete set of debug information for those researchers than they could obtain from the actual hardware. SimOS has also been used in the research of workload characterization, such as the characterization of the Sybase database [40]. Other studies performed with the aid of SimOS include the breakdown of operating system execution time on today's processors as opposed to tomorrow processors [41], in the evaluation of different organizations of chip multiprocessors [39], and the evaluation of the system performance on large commercial workloads [6].

2.5.3: SimOS versus our Emulator.

The SimOS simulation environment differs from the emulation tool developed during this research in two different ways. The first is that the two have very different target application domains. The SimOS system studies both high performance and general purpose systems. The emulator developed for this research was created to study embedded systems.

The second difference is the system characteristics that each studies. Being created to study high-performance and general purpose systems, SimOS studies mainly end-to-end performance. The emulator developed during this research was created to evaluate the real-time performance of low power embedded processors, such as measuring the difference between the invocations of periodic tasks, measuring if they are either early or late, and measuring the reaction time from external interrupts or stimuli.

## Chapter 3: The Emulator

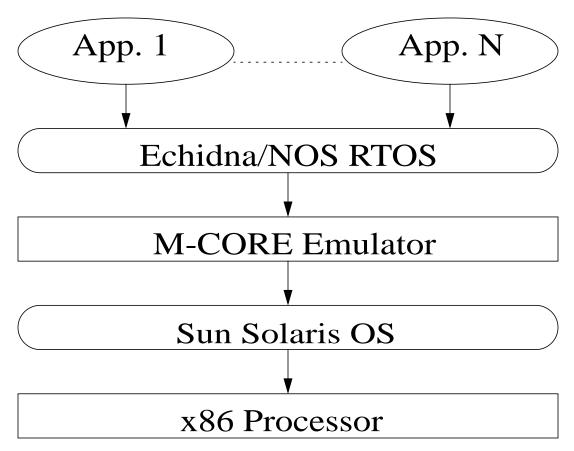

For this project, Motorola's M-CORE architecture was used as the model architecture for our emulator. This architecture was chosen because the M-CORE architecture is one of the cutting edge embedded processors on the market today, and the M-CORE was designed for high performance and low power operation [37]. In this chapter, first the M-CORE architecture is described, followed by the specifics of the emulator, how it works, what information it takes as an input, how it processes that information, and what information it outputs during the emulation. Finally, the method used to validate the emulator is described. Figure 2 shows a system view of the emulator and both the hardware and operating system that it is running on and the Real-Time Operating System and applications that are running on it.

### 3.1: M-CORE Architecture

The Motorola M-CORE architecture is a 32-bit Load/Store architecture with a fixed 16-bit instruction length and 32-bit data length. Figure 3 shows all of the available instruction formats in the M-CORE architecture. It has a 16 entry 32-bit general register file, a 16 entry 32-bit alternate register file to allow fast interrupt support, and a 13 entry control register file accessible only by the supervisor mode. Its execution pipeline's four stages are completely hidden from the application software. Most instructions execute in a single cycle with two cycle execution for loads, stores, and taken branches and

Figure 2: The Emulation Environment.

This figure shows the emulation environment developed in this work for real-time system evaluation. The emulator runs on top of the Sun Solaris Operating System, running on top of a x86 Processor. On top of the emulator is run the target Real-Time Operating System, either Echidna or NOS. On top of the RTOS, the benchmark applications are run.

jumps. The address space is byte, halfword, and word addressable, and allows both fast

and normal interrupts, allowing those interrupts to be either vectored or autovectored

interrupts.

The pipeline for the M-CORE consists of four stages: instruction fetch, instruc-

tion decode/register file read, execute, and writeback. All of these stages operate simul-

taneously, making single cycle instructions possible. All sixteen general purpose

| 15           |         | 4          | 3        | 0 |

|--------------|---------|------------|----------|---|

| .)           | OPCODE  |            |          |   |

| <u>15</u>    | 8       | <u> </u>   | 3        | 0 |

| OPCO         | OPCODE  |            | RX       |   |

| 15           | 5 98 43 |            |          | 0 |

| ) OPCO       | DDE     | IMM5       | RX       |   |

| 15           | 98      | 4          | 3        | 0 |

| OPCC         | DDE     | OIMM5      | RX       |   |

| 15           | 11 10   | 4          | 3        | 0 |

| ) OPCODE     | I       | MM7        | RX       |   |

| 15           | 98      | 4          | 3        | 0 |

| OPC0         | DDE     | CREG       | RX       |   |

| <u>15 12</u> | 11 8    | <u>7</u> 4 | 3        | 0 |

| ) OPCODE     | RZ      | IMM4       | RX       |   |

| 15           |         | 4          | 3        | 0 |

| OPCODE       |         |            | RX       |   |

| 15 12        | 11 0    | 57         |          | 0 |

| OPCODE       | RZ      | DIS        | SP_8     |   |

| 15           | 11 10   |            |          | 0 |

| OPCODE       |         | DISP_11    |          |   |

| 15           |         | 4          | 3        | 0 |

| )            | OPCODE  |            | RX       |   |

| 15           | 8       | 57         |          | 0 |

| 15           |         |            | 0 0      |   |

| OPCO         | DDE     | DIS        | SP_8     |   |

| 0 0PC0       |         |            | <u>3</u> | 0 |

# Figure 3. Instruction Format.

The above figure shows all 13 of the possible instruction formats for the M-CORE architecture. The first six instruction formats are register to register instructions, and they are: (a) Monadic Register Addressing, (b) Dyadic Register Addressing, (c) Register with 5-Bit Immediate, (d) Register with 5-Bit Offset Immediate, (e) Register with 7-Bit Immediate, and (f) Control Register Addressing. The next three are data memory access instructions, and they are: (g) Scaled 4-Bit Immediate Addressing, (h) Load/Store Register Quadrant and Multiple Register, and (i) Load Relative Word. The last four formats are flow control instructions, and they are: (j) Scaled 11-Bit Displacement, (k) Register Addressing, (l) Indirect, and (m) Register with 4-Bit Negative Displacement.

registers can be used as source operands and instruction results (i.e. it is an orthogonal register file).

The architecture's execution unit contains the following sub-units: A 32-bit ALU, a 32-bit barrel shifter, a find-first-one unit, a multiplication/division unit, and result feeding forward hardware. All arithmetic instructions are single cycle instructions with the exception of the multiply and signed and unsigned divide instructions. The multiply is implemented with a 2-bit per cycle Booth algorithm, and the divide instruction's timing is also data dependent.

The program counter (PC) unit has a PC incrementer and a dedicated branch address adder. This minimizes the change of instruction flow delays to only a single pipeline bubble delay, for the branch target addresses are calculated during the instruction decode phase. If a branch is not taken, no delay is incurred.

Byte, halfword, and word memory accesses are provided with this architecture, with an automatic zero-extension of bytes and halfwords. Single memory accesses, independent of size, execute in two cycles. Multiple memory accesses, such as the Load Multiple instruction, or the Store Quadrant instruction, can execute in a number of cycles equal to the number of words transferred plus one.

The M-CORE programming model is defined for two privilege modes: supervisor and user mode. There are certain operations not available in user mode. User programs can only access registers in the general register file, whereas supervisor mode programs can access all registers, using control registers to perform supervisory functions. User programs are prohibited from accessing privileged information (the control registers, vector offset table, settings for I/O, etc.). If a user program tries to access priv-

ileged information or tries to execute a privileged instruction, a privilege violation exception occurs. A single bit (the S bit) in the Program Status Register(PSR) determines which mode the architecture is currently running in.

This architecture uses the user programming model during normal user mode operation. During exception and interrupt processing, the processor changes over from user mode to privileged mode. Exception processing saves the current values of the PC and the PSR, and then sets the S bit in the PSR, and loads the new PC from the exception vector table. During the return from exception (rfe) instruction (or return from fast interrupt (rfi) instruction for fast interrupts) the original PC and PSR values from before the exception are restored, and execution continues in the user mode.

There are thirteen control registers in the M-CORE architecture that can only be accessed during the supervisor mode. These include the PSR as mentioned above, the Vector Base Register (VBR) holding the base address used in the calculation of exception handler PCs, an Exception Program Status Register (EPSR) and Exception Program Counter (EPC), to store the PSR and PC during exceptions, a Fast Interrupt Program Status Register (FPSR) and Fast Interrupt Program Counter (FPC), to store the PSR and PC during fast interrupts, five scratch registers for supervisor software to use during the handling of exceptions, and two registers are used for global control and status. Both the user programming model as well as those resources that are available during supervisor mode can be seen in Figure 4.

The M-CORE supports two's-complement data formats, and instructions either explicitly encode the operand size in the instruction (load/store) or implicitly define it for the instruction operation (index operations, byte extraction). Memory is viewed

| RO  | Stack pointer     |                |                 |             |

|-----|-------------------|----------------|-----------------|-------------|

| R1  | Volatile          |                |                 |             |

| R2  | Volatile, 1st arg | RO'            |                 |             |

| R3  | Volatile, 2nd arg | R1'            |                 |             |

| R4  | Volatile, 3rd arg | R2'            | CRO             | PSR         |

| R5  | Volatile, 4th arg | R3'            | CR1             | VBR         |

| R6  | Volatile, 5th arg | R4'            | CR2             | EPSR        |

| R7  | Volatile, 6th arg | R5'            | CR3             | FPSR        |

| R8  | Non-volatile      | R6'            | CR4             | EPC         |

| R9  | Non-volatile      | R7'            | CR5             | FPC         |

| R10 | Non-volatile      | R8'            | CR6             | SS0         |

| R11 | Non-volatile      | R9'            | CR7             | SS1         |

| R12 | Non-volatile      | R10'           | CR8             | SS2         |

| R13 | Non-volatile      | R11'           | CR9             | SS3         |

| R14 | Non-volatile      | R12'           | CR10            | SS4         |

| R15 | Link register     | R13'           | CR11            | GCR         |

| K15 | Link register     | R14'           | CR12            | GSR         |

| PC  | Program counter   | R15'           |                 |             |

| 10  | r rogrum counter  | Alternate file |                 |             |

|     | С                 | (b) Super-     | visor Additiona | l Resources |

Figure 4: User Program Model and Supervisor Additional Resources. The above figure shows both the limited resources available during user mode execution as well as the additional resources available during supervisor mode execution. In (a), it can be seen that the user mode programs can use any of the sixteen general purpose registers, access the Program Counter, and the Carry bit. In supervisor mode (b), the alternate register file can be accessed, as well as all of the control registers.

from big-endian perspective, meaning the most significant byte (byte zero) of word zero

is located at address zero.

There are ninety-eight instructions for the M-CORE architecture. A table of

these can be found in Appendix A (Table A-1).

All of the information in the above section has been obtained from [36, 37, 38, 52].

# 3.2: Emulator Parts

The emulator for the Motorola M-CORE was written entirely using the C programming language and can be broken down into several distinguishable parts. The sections following look at each of those points in detail. Section 3.2.1 describes the method for bringing in the program to be run on the emulator using the ELF file format. Section 3.2.2 describes the mechanisms used to store and retrieve information in the main memory and the general purpose registers. Sections 3.2.3-3.2.6 describe the pipeline. In the emulator, the pipeline is instantiated in reverse order, that is, write back first, then execution, then decode, and finally fetch. The order does not matter since all stages are taking place simultaneously, but ordering the phases this way in C allows for easier handling of data transfer as well as for exception processing. Section 3.2.7 describes all of the post stage maintenance that needs to be maintained every cycle, specifically maintaining the timer, checking for interrupts, and handling exceptions. Section 3.2.8 describes the optional output of the simulator. Finally, Section 3.3 describes the method used to validate the emulator.

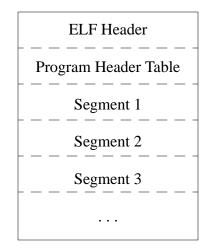

#### 3.2.1: ELF Input

The emulator takes as its input the executable and linking format (ELF) file that is produced by the compiler. An ELF file, like any other compiler output file, contains all of the information necessary to run a program on its target hardware. The ELF file contains sections of data called program segments that are blocks of data to be placed directly into the M-CORE's memory at locations also given in the file as physical

Figure 5: Format of an ELF file.

This figure shows the breakdown of an ELF file. The first group of information is the ELF Header. This data will contain the location of the Program Header Table. The Program Header Table gives information about the programs segments: How many are there, where are they located in this file, and were do they need to be placed in the target systems memory map.

addresses. Each one of these areas are given as either read-only (code), or read-write (such as the stack and the heap). Writing to either an undefined area of memory, or to a read-only section causes an exception. See Figure 5 for an overview of the ELF file format. The emulator uses a separate executable C program that brings the ELF file in, parses it, and creates a file the emulator can read. This file contains a translation map consisting of the start address, final address, and offset for each block of memory — and the actual data itself. During emulator start up, this file is brought in, the translation map is loaded, and the data is placed into the memory storage device (described in 3.2.2).

# 3.2.2: Main Memory and Registers

Given the four gigabytes of addressable memory space in the M-CORE architecture, it is both impossible and unnecessary to store the entire addressable memory space in an array. Instead, the emulator stores smaller segments of that addressable space, located in arrays, and institutes a method of accessing locations in memory through a translation map. For example: A load instruction wishes to load a word from memory location 'x'. From looking in the translation map, the emulator finds that address 'x' falls between locations 'w' and 'y'. The associated offset to values that fall between 'w' and 'y' is 'z'. Therefore the data at that memory location can be found in the memory array using an index of 'x'-'z'.

Since the M-CORE architecture uses memory mapped devices, the emulator uses two main memory structures, one for values sent to and from the physical memory and one for values sent to and from the memory mapped devices such as I/O and the timer. The first structure, OnChipRam, is the physical memory. This is where the data brought in from the ELF file is placed. The second structure, OnChipMapRam, is an array containing all locations in the memory map that correspond to memory mapped devices, such as the exception vector table, interrupt registers, timer registers, and I/O devices.

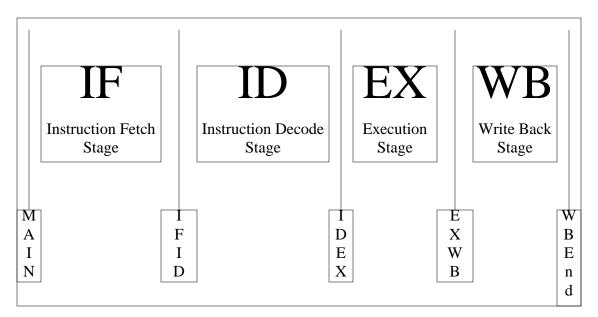

Other values that need to be stored, beside the above mentioned memory arrays, the sixteen member 32-bit register file, its shadow register file, and the control register file, are the PC value and instruction before and after each stage. Therefore the emulator has five pairs of registers: MAIN and MAINpc store the values about to enter the pipeline, IFID and IFIDpc store the values between the Instruction Fetch and Instruction Decode stages, IDEX and IDEXpc store the values between the Instruction Decode and Execution Stages, EXWB and EXWBpc store the values between the Execution and Write Back stages, and WBEnd and WBEndpc stores the values leaving the pipeline.

Figure 6: The M-CORE pipeline.

The above diagram shows the M-CORE pipeline. It consists of four stages: Instruction Fetch, Instruction Decode, Execution, and Write Back. Between each of the stages and at the beginning and end of the pipeline there are pairs of registers that hold information between cycles. These registers are MAIN & MAINpc, IFID & IFIDpc, IDEX & IDEXpc, EXWB & EXWBpc, and WBEnd & WBEndpc.

# 3.2.3: Write Back Stage

In the emulator, since the majority of the assignments are done in the execution stage, the only operation that occurs during this stage is the moving of PC and instruction values from the EXWB registers before this stage to the WBEnd registers following this stage. This stage's purpose is to show which instruction is currently in the write back stage of the pipeline.

# 3.2.4: Execution Stage

Both instruction execution and assignment take place during this stage. All of the instruction execution code for each instruction is placed into a function of the same name as that instruction. All of these instructions are then mapped into an array of functions, indexed by the opcode. The first level of the function array is indexed by the most significant four bits in the opcode. If these first four bits are enough to determine which instruction is to be executed, then that instruction's function is immediately called. If not, a second level function array is indexed with the second four most significant bits of the opcode, and so on. On the average, only the first two function pointers need to be indexed before the instruction has been found, greatly improving upon the worst case performance of a 98 element if-then-else-if-then-else/switch statement.

Once the function is called, the instruction is executed. It is also important to note here that during this phase the divide instructions check for possible divide-by-zero exceptions and the load and store instructions check for misaligned access to memory exceptions. Another important point to make here is that there are instructions that take more than one cycle to execute, such as loads and stores, branches, and multiplies and divides. If the instruction executing is one that takes more then one cycle, a stall variable is set with the number of bubbles that need to be inserted into the pipeline.

After executing the instruction, if the stall variable is still zero, the PC and instruction values for the execute phase are moved to the EXWB registers. However, if the stall variable is not zero, the PC and instruction values are not passed on, since they do not leave this stage (they are still executing). It is also important to note that if the stall variable is greater than zero during the beginning of this stage, no instruction will execute since the instruction currently in the stage is the one that caused the stall and has already executed.

# 3.2.5: Instruction Decode Stage

The instruction decode phase is almost as important as the execution phase in that it also checks for a number of exceptions that can happen during the decode stage.

These exceptions are the illegal instruction exception, the privilege violation exception, and the four different trap exceptions. It is important to catch these exceptions here because they must not be allowed to reach the execution phase. If the exception occurs here, the instruction in this stage must be flushed and exception handling must begin.

At the end of this stage, like the end of the execution stage, the PC and instruction values are moved to the IDEX registers if the stall variable is set to zero. If not, it is assumed that this instruction is stalled here while waiting for the instruction executing in the execution stage to finish. Also, the exception check is not made if the stall variable is greater than zero (since this check already occurred when the instruction originally got to this stage).

3.2.6: Instruction Fetch Stage

During this stage, the instruction is fetched from memory, and passed to the IFID registers. Again, however, this only occurs when the stall variable is set to zero.

3.2.7: Post Stage Maintenance

After all of the stages have completed, there are a few tasks that need to be performed before the emulator can continue onto the next cycle. Specifically, if the timer needs to be incremented, that needs to be completed. Also, a check must be made to verify that no interrupts are waiting to happen. Finally, if an exception has occurred, state needs to be saved, and the exception handler needs to be started.

3.2.7.1: The Timer

The timer described in the M-CORE documentation sets off a timer interrupt every 0.1 seconds. Since the emulator is modeling a 20MHz processor, that means that every 2 million cycles there needs to be a timer interrupt. A timer tick variable (two

bytes) is set, and every time that the variable overflows, an interrupt occurs. The variable flows from a start value of 0x0bdb and continues to 0xffff. This calculates to 62,500 "ticks". Dividing this value into 2 million cycles determine that every 32 cycles, the timer tick value needs to be incremented. Therefore, every cycle, a check is made. If it has been 32 cycles since the last timer tick increment, the timer tick is incremented. If when this occurs, the timer tick overflows, the timer tick is set back to 0x0bdb (0xFFFF-62,500), and a timer interrupt is signaled by the emulator [36]. Since this description of the timer is very straight forward and easy to program in C, this is how the emulator implements the timer.

3.2.7.2: Interrupts

The Motorola M-CORE architecture allows for both fast and regular interrupts to occur. The difference between a fast and a regular interrupt is that a regular interrupt can be interrupted (by a fast interrupt) while a fast interrupt cannot. To determine whether an interrupt has occurred, every cycle the M-CORE architecture does a bitwise AND between two registers: the interrupt source register (the fast interrupt source register for fast interrupt and the regular interrupt source register for regular interrupts), which will contain all zeros, unless there is an interrupt enable register for fast interrupt enable register (the fast interrupt source for fast interrupt enable register (the fast interrupt), which is set by the supervisor, determining which interrupts will be serviced, and which will be ignored.

If the ANDing of these two registers returns any value other than zero, an interrupt occurs. The interrupt number is then determined and from that number a vector offset is then determined and sent to the exception handler. Interrupts are handled by the

exception handler. The only difference is the method in which they are detected, and that the interrupt vector offset is sent to the exception handler [36, 37, 38]. Being that this is very straight forward and easy to program in C, this is how the emulator implements interrupts.

#### 3.2.7.3: Exceptions

In the M-CORE architecture, if either an exception or an interrupt has occurred, a flag is set showing that an exception (or interrupt) has happened and needs to be handled. The first thing that occurs is that both the current PC and PSR values are saved to either the EPC and EPSR registers (for exceptions and regular interrupts) or the FPC and FPSR registers (for fast interrupts). The PC value that is stored is determined by what type of interrupt or exception that is happening. If it is an exception that occurred during the instruction decode stage, the PC for the instruction in the decode stage is stored. Likewise, if the exception was a divide-by-zero or misaligned access in the execution stage, the PC of that instruction is saved. However, if a misaligned access occurred during the calculation of either a jump to subroutine immediate (jsri) or jump immediate (jmpi) instruction, the PC value fetched is the value that is stored. All of the instructions in the pipeline behind the instruction that caused the exception are flushed. However, all the instructions further along in the pipe are allowed to complete.

If an interrupt caused the exception handler to start, the PC value stored is the PC after the instruction that is in the instruction fetch stage. So whenever an interrupt occurs, it allows all instructions in the pipe to complete before beginning the exception handler.